はじめに

昨日の「Intel Quark SoC X1000自体の仕様」に続いて、今日はIntel QuarkのプロセッサーコアIPである「Intel Quark Core(以下、Quark Core)」について書いてみたいと思います。

80386でもPentiumでもない

先日「Intel Quarkの正体は80386?それともPentium?」で、Quark Coreが80386だという説とPentium(P54C)だという説の2つの記事を紹介して、私はPentiumだという後藤弘茂さんの説を支持しました。正確にはフルシンセサイザブルだということなので、Pentiumそのものではないだろうと思い、「Pentiumベースである」という書き方にしてはいますが、要するにPentium系だろうと考えていました。

しかし、比較対象はPentiumではなくIntel DX4(あるいはIntel 486DX4と呼ばれる)とすべきでした。Quark CoreはIntel DX4に対して、現在のOSやアプリケーションに必要とされる命令と、セキュリティ上の後退をもたらさないための拡張を加えたプロセッサーコアIPです。

Intel DX4とQuark Coreを比較して気になった点を以下に挙げてみます:

- 命令セットがPentium ISA互換に拡張されている。

- 命令セットの拡張に合わせてPentium以降のCPUに採用されているTSC(Time Stamp Counter)とMSR(Model Specific Register)をサポートしている。

- MSRはPentium互換。

- CPU IDは、Family ID = 0x5、Model = 0x9, Stepping ID = 0x0で、Pentium(P5)ファミリーのPentium processor with MMX Technologyの1個先のモデルのIDを持つ。ただし、MMXのサポートはない。

- パイプラインはIntel DX4と同じ基本5ステージ構造。

- 最大クロック周波数は533MHz。

- Intel DX4時代には存在していなかったPAE(Physical Address Extension)とXD(eXecute Disable)ビットとSMEP(Supervisor Mode Execution Protection)に対応している。ただし、アドレスはIntel DX4と同様に32ビットである。

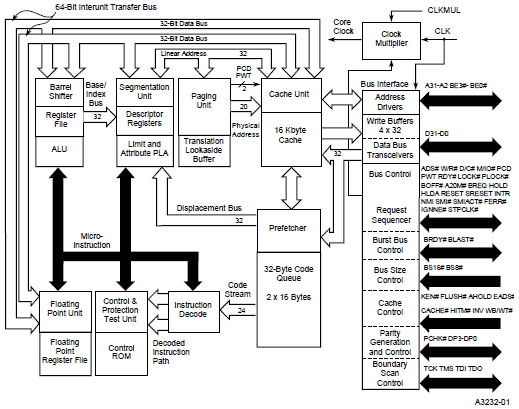

以下にIntel DX4とQuark Coreのブロックダイアグラムを引用します:

Intel DX4のブロックダイアグラム

EMBEDDED WRITE-BACK ENHANCED IntelDX4™ PROCESSOR(October 1995 Order Number: 272771-001)より引用

Quark Coreのブロックダイアグラム

Intel Quark SoC X1000 Core Hardware Reference Manualより引用

このように、基本構造はIntel DX4をほぼそのままとしたうえで、現在のOSやアプリケーションの要求に耐えられるように拡張されたマイクロアーキテクチャとなっています。回路の規模はPentiumよりもかなり小さく、無理のなく低消費電力のプロセッサーコアIPとして使用できるものに仕上がっています。

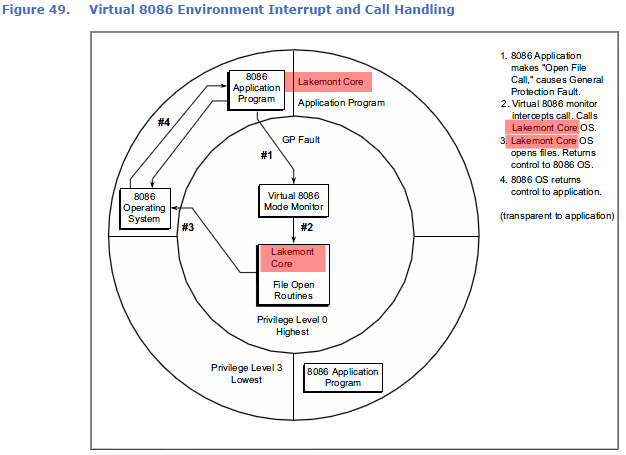

コードネームまたはマイクロアーキテクチャ名はLakemont Core?

この新しいマイクロアーキテクチャは「Lakemont Core」という名前なのかもしれません。なぜかというと資料の一部に「Lakemont Core」との記載が残っているからです。例えば「Intel Quark SoC X1000 Core Developer’s Manual(October 2013 Order Number: 329679-001US)」の111ページに掲載されている「Figure 49. Virtual 8086 Environment Interrupt and Call Handling」をよく見ると「Lakemont Core」と書いてあります。

以下に該当する図を引用します(赤色強調は筆者による):

このようにこの図の中には4か所も「Lakemont Core」との記載があります。

おそらく一括して「Lakemont Core」を「Intel Quark Core」に置き換えたときに、該当する図が特殊な文字コードだったために(→詳しくは「“Lakemont Core”が見つかりにくかった理由」を参照ください)そのまま残ってしまって見過ごされたのでしょう。

一応Wikipedia英語版の「List of Intel codenames」なども当たってみたのですが、該当するコードネームは記載がありませんでした。→2014年5月29日追記:Lakemont Coreがコードネームであると確定しました。

実際どうなのかわかりませんが、現状ではそういう情報をいろいろと検索しても見つけられませんでしたので、「Lakemont Core」が当たりなら、ここでの、この指摘が初出になるかと思います。→後日談

Intel Quark Coreの仕様

さて、主な仕様の紹介も、Intel Galileo Boardから始めて、Intel Quark SoC X1000と紹介してきましたが、今回はIntel Quark SoC X1000のプロセッサーコア部分であるIntel Quark Coreの仕様を抜粋して紹介したいと思います。なお、抜粋仕様に含まれる性能や主張はIntel発表そのままであり、筆者の主張ではありませんので、その点はご理解ください。

主な仕様

Intel Quark CoreはIA-32アーキテクチャのために書かれた、さまざまな既存のアプリケーションを実行できる安価で高性能な組み込みシステムのデザインを可能にします。

Intel Quark Coreは16キロバイトのユニファイドキャッシュと性能向上のためのオンチップの浮動小数点演算ハードウェアを統合しています。

Intel Quark Coreはモバイルおよび組み込みコンピューティングのための低消費電力「SL Technology」が組み込まれています。SL Technologyは性能に影響を与えずにEPA(米国環境保護庁)のエナジースタープロジェクトガイドラインを満たしたシステムの設計を可能にします。これにより、すべてのIntel Quark Coreベースのハンドヘルド用途へのシステム設計を容易にし、電池寿命を伸ばします。SL Technologyはシステムデザイナーに様々な異なる低消費電力(電池寿命を延ばす特性)への要求に合わせることができるように、パワーマネージメントスキームを提供します。

Intel Quark Coreはアプリケーションとオペレーティングシステムソフトウェアに透過的な消費電力管理機能を提供します。クロック停止、自動HALTパワーダウン、および自動アイドルパワーダウンは、プロセッサーパワーマネージメントのソフトウェア透過な制御を可能にします。

同様に重要なのは、プロセッサーがシステム消費電力を管理する能力です。Intel Quark Core System Management Mode(SMM)は、システム管理コードのためにマスク不可能なシステムマネージメント割り込み(SMI#)、対応するResume(RSM)命令、および新しいメモリスペースを組み込んでいます。※1 Intel SMMはあらゆるアプリケーションやオペレーティングシステムに対して透過的に、プロセッサーコアのシームレスなパワー制御、システムロジック、メインメモリおよび1つ以上の周辺機器を制御する手段を確保します。

Intel Quark Coreの特徴

Intel Quark Coreは32ビットの整数演算処理装置、内蔵キャッシュおよびメモリ管理機構から構成されます。

- 32ビットRISC整数演算コア – Intel Quark Coreは完全な幅を持つALUと8個の汎用レジスターを使用して、8ビット、16ビットおよび32ビットのデータタイプで算術演算と論理演算の完全なセットを実行する。

- 1サイクル実行 – 多くの命令が1クロックで実行できる。

- 命令パイプライン – Intel Quark Coreでは、フェッチ、デコード、アドレス変換および命令の実行をオーバーラップする。

- オンチップの浮動小数点演算ユニット – Intel Quark CoreはIEEE標準754に定義された、32ビット、64ビットおよび80ビットのフォーマットをサポートする。このユニットは8087、Intel 287、Intel 387コプロセッサーおよびIntel OverDriveプロセッサーとバイナリーレベルで互換性がある。

- キャッシュコヒーレンシー※2をサポートするオンチップのキャッシュ – 16キロバイトの内部キャッシュは命令とデータの両方で使用する。外部キャッシュコントローラーがキャッシュの一貫性を維持できるように、内部キャッシュを無効にするか、またはフラッシュさせることができる。

- 外部キャッシュコントロール – プロセッサーがキャッシュの一貫性を維持できるように、外部キャッシュに対するライトバックとフラッシュの制御を提供する。

- 注釈:

- Intel Quark SoC X1000におけるIntel Quark Coreの実装は外部キャッシュコントロールを提供しない。

- オンチップメモリ管理ユニット – アドレス管理とメモリスペース保護メカニズムはマルチタスクと仮想メモリ環境における、メモリの整合性を維持する。メモリ管理ユニットはセグメンテーションとページングの両方をサポートする。

- バーストサイクル – バースト転送はそれぞれのバスクロックサイクルごとにメモリから新しいダブルワードの読み出しをすることを可能にする。この機能は特に命令プリフェッチと内部キャッシュを埋めるのに役立つ。

- ライトバッファー – プロセッサーには、連続したメモリへの書き込み性能を向上させるために4つのライトバッファーを含む。プロセッサーは書き込みをこのバッファーへ行った後に外部のバスへの書き込みが終了することを待たずに処理を継続することができる。

- バスバックオフ – 別のバスマスターがプロセッサー主導のバスサイクル中にバスの制御を必要とするのであれば、Intel Quark Coreはバス信号をフロートにし、再びバスを利用可能にするサイクルを開始する。

- 命令再実行 – メモリへのアクセスの試みが失敗した際に発生する例外のあとに、プログラムは実行を続けることができる。これはページ単位での仮想メモリへの応用に用いることができる。

- ダイナミックバスサイジング(動的なバス幅変更) – 外部のコントローラーは動的にデータバスの有効幅を変更することができる。バス幅は8ビット、16ビットまたは32ビットを使用することができる。

- 注釈:

- Intel Quark SoC X1000におけるIntel Quark Coreの実装はダイナミックバスサイジングを提供しない。常に32ビット固定である。

SL Technologyは以下の特徴を提供します:

- Intelシステムマネージメントモード – ユニークなIntelアーキテクチャの動作モードは、オペレーティングシステムとアプリケーションに完全に透過な方法で、インテリジェントなパワーマネージメントと他の拡張機能を使用できる占有された専用の割り込みとアドレス空間を提供する。

- I/Oリスタート – System Management Interrupt(SMI#)によって割り込みをかけられた入出力命令は、

RSM命令の実行に続いて自動的に再開される。 - 自動HALTパワーダウン – プロセッサーが自動HALTパワーダウン状態に入るために、

HALT命令の実行後にIntel Quark Coreは通常のHALTバスサイクルを発行し、Intel Quark Coreへのクロックは自動的に停止する。

エンハンスバスモードの特徴(Write-Back Enhanced Intel Quark Coreプロセッサーのみ対応):

- 内部キャッシュへのライトバック – Write-Back Enhanced Intel Quark Coreは、ユニファイドキャッシュに対するライトバックのサポートが追加される。内蔵キャッシュは1行単位でライトバックかライトスルーかを指定できる。内部キャッシュは調整されたMESIプロトコルを実装する。これはシングルプロセッサーのシステムに最適化されている。

- エンハンスバスモード – 新しいエンハンスバスモードをサポートするために、いくつかの信号の定義を変更した(ライトバックモード)。

- ライトバースト – プロセッサーからメモリへのデータの書き込みを、ゼロウエイト状態でバースト転送することができる。

まとめ

Intel Quark CoreはPentiumではなく、Intel DX4をベースとするプロセッサーコアを、現代のソフトウェア要求に合うように拡張したものです。

このようになかなかユニークなコアなのですが、最初の製品は学習用がメインのマイコンボードという状況です。これがメインの使用目的ではないことは明らかですから、いずれ本来のIoT(Internet of Things)な使われ方がされるはずです。しかし、IoTというジャンルそのものがまだ立ち上がったとはいえない状況です。

IoTではGoogle Glassや腕時計(iWatch?)のようなものがよく話題に上りますが、実際にはもっと地味だけれど生活に欠かせないものがメインになってくる可能性もあるのではないかと思います。たとえばそれは医療(ヘルスケア)分野です。Quarkも妙に堅牢性に力が入っているところを見ると、医療向けの機器に組み込むつもりで設計されていたのではないか、という気もします。Intelにはヘルスケアソリューションを扱う部門があり、そう考えると、その分野には強力な処理能力が不要で、小さく、消費電力が少なく、堅牢性の高いプロセッサーが必要なものがいろいろと思い浮かびます。そうした分野向けに作られていたのでは…と、ちょっと考えてしまいます。

しかし、IoT。本当のところ、どんな製品が出てくるのでしょうね? その時採用されているのは、Intelアーキテクチャか、ARMか。本当に結果を見るのが楽しみです。

2013年12月1日更新

- 訂正を行う際に元の文章を残した上で追記を行ってきましたが、そういった箇所が増えて読みづらくなったため、最新の正しい記述を残して訂正前の文章を削除しました。

- 2013年12月1日時点で判明している情報を仕様関連に反映しました。

2014年1月9日更新

- SMEP(Supervisor Mode Execution Protection)をサポートしていることを追記しました。

情報と図の出典および引用元

- 「Intel Quark SoC X1000 Core Hardware Reference Manual(October 2013 Order Number: 329678-001US)」

「Intel Quark SoC X1000 Core Developer’s Manual(October 2013 Order Number: 329679-001US)」

Intel Makers Community : Intel Quark SoC Documentsよりダウンロード可能 - 1997年6月にIntelが発行したPentium Processorに関する文書(

Order Number 241997-010)※PDF

参考文献

Pentiumの復習のために以下の文献を参考にしました。

- MMXテクノロジオフィシャルガイド

著・インテルジャパン株式会社 菅原清文

1997年1月31日 初版

ソフトバンク株式会社 出版事業部

9784797301977 1910055029002

関連記事

- Intel Galileo(Fab D)とKips Bay Fab Cとの違い

- Intel Quark関連コードネームまとめ

- Intel Galileo BoardやKips Bayのファームウェア更新について

- Intel Quark Core(Lakemont Core)はPentiumベースではない

- 2013年12月中旬よりIntel Galileo Board国内販売開始

- Intel Galileo BoardとQuarkに関するまとめ(勝手にFAQ)

- Intel Quark SoC X1000自体の仕様

- Intel Quark SoC X1000搭載Intel Galileo Boardを発表

- Intel Quarkの正体は80386?それともPentium?

- 現在のIA-32に搭載されているSMMと同じモード。Intel 80386とIntel 486の一部から搭載されたもので、全製品に搭載されたのはPentiumからだった。

- プロセッサーコアあるいはキャッシュシステムがシステムに複数存在するときに、キャッシュの一貫性を保つことをキャッシュコヒーレンシーという。