はじめに

昨日の「Intel Quark SoC X1000搭載Intel Galileo Boardを発表」では「Intel Galileo Board(以下、Galileo)」としての仕様についていろいろと書きましたが、今日はGalileoから離れて「Intel Quark SoC X1000」自体の仕様について抜粋して紹介したいと思います。なお、抜粋仕様に含まれる性能や主張はIntel発表そのままであり、筆者の主張ではありませんので、その点はご理解ください。

主な仕様

Intel Quark SoC X1000はセキュアで低電力消費となるように設計された、組み込み分野向けのIntel Architecture SoC(以下、SoC)です。セキュアな利用を可能にするために、SoCにはオンダイで統合されたブートROMを持ちます。ブートROMは外付けの場合と異なり、リセットから起動する際に信頼できるコードだけが実行されることを確実にします。このブートROMによって、外部のファームウェアが改変されていないかの認証を行い、その後に処理を移すといったことができます。SoCは、標準の8ビットDDR3メモリを使用する場合に限り、ECCによる保護のサポートを提供します。

また、SoCは低レイテンシーが重要となるシステムメモリのために、DRAMにオーバーレイを構成できる512キロバイトのオンダイSRAM(eSRAM)を搭載しています。また、オンダイのeSRAMは信頼性のためにECCによる保護が提供されます。

※ブートROMとECCのサポートの有無はSKUによります。

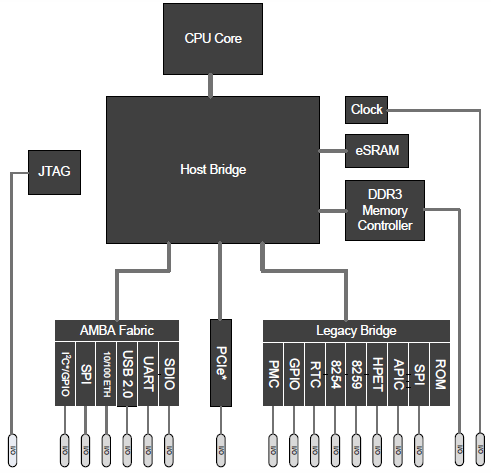

これらを含めたブロック図を以下に示します:

SoCに含まれるCPUコアの特徴

- 最大400MHzの動作クロック

- 低消費電力のためのオプションとして、最大クロックの1/2または1/4での動作

- 32ビットアドレスバス、32ビットデータバス

- 16キロバイトの命令とデータでの共有L1キャッシュ

※さらに詳しいプロセッサーコアIPの情報は別稿「Intel Quark Core自体の仕様(コードネームはLakemont Core?)」にまとめました。

システムメモリコントローラーの特徴

- ECCをサポートするシングルチャネルDDR3メモリコントローラー

- 16ビットデータバス

- 最大2ランクまでサポート

- DDR3による800MT/sのデータレートをサポート

- 8ビットのデータ幅のDRAM

- 1ギガビット、2ギガビット、4ギガビットのDRAMに対応

- 性能の最適化のために、異なるバンクアドレスの物理的なマッピングをサポート

- 性能を向上させるためのアウトオブオーダー処理※1

- 電力消費を抑えるためのアグレッシブなパワーマネージメント

- 未使用のページをクローズするための積極的なページクローズポリシー

- DRAMデバイスの下へのはんだ付けをサポート

組み込みSRAMの特徴

- 低レイテンシーのオンダイ統合された512キロバイトのSRAM

- 512キロバイトのブロック、または個々の4キロバイトページのシステムメモリへのオーバーレイのいずれかに構成が可能

- ECCによる保護

パワーマネジメントの特徴

- ACPI 3.0仕様をサポート

- C0、C1、C2プロセッサーパワーステート

- S0、S3、S4/S5システムパワーステート

セキュリティの特徴

- オンダイのブートROMが提供されることにより、ハードウェアRoot of Trust(RoT)のためのファームウェア認証が可能※2

PCI Expressの特徴

SoCにはPCI Express Rev 2.0仕様による最大2.5GT/sのデータ転送速度をサポートする、2つのPCI Expressルートポートがあります。それぞれのポートは1xリンクとして構成されています。

- 64バイト単位でリクエストを分割することが可能な、最大128バイトのペイロードサイズ

- ソフトウェア主導によるリンクパワーマネージメント(D1、D2、D3Hot、L1ステート)

- PMEイベントの生成

Ethernetの特徴

- データ転送速度が10または100Mbpsとなる、外部のFast EthernetのPHYとRMIIインターフェースで接続

- 全二重動作:

- IEEE 802.3x フローコントロールのサポート

- ユーザーアプリケーションへの受信した「ポーズコントロールフレーム」のオプションの転送

- 半二重動作:

- CSMA/CDプロトコルのサポート

- フレキシブルアドレスフィルタリングモード

- 64ビットのハッシュによるマルチキャストおよびユニキャスト(DA)アドレスのフィルター

- 全てのマルチキャストアドレスフレームを通過させるオプション

- ネットワークのモニタリングのためにまったくフィルタリングせずにすべてのフレームを通過させるプロミスキャスモード

- 状況報告のために入ってくるパケット(フィルターに従う)を全て通過

- 最大1522バイトまでの長さに変更可能な標準Ethernetフレームをサポート

- IPv4ヘッダーのチェックサム、IPv4またはIPv6データグラム(Type 2)でカプセル化されたTCP、UDP、ICMPチェックサムを検証する拡張受信モジュール

- IEEE1588-2002とIEEE1588-2008に記載のある、Ethernetフレームへのタイムススタンプ記録をサポート。各フレームの転送または受信ステータスで64ビットのタイムスタンプを付与。※3

- High-Speed(480Mbps)、Full-Speed(12Mbps)、Low-Speed(1.5Mbps)動作をサポートする2つのホストポート

- EHCIとOCHIホストコントローラー

- High-Speed(480Mbps)とFull-Speed(12Mbps)動作をサポートする1つのデバイスポート※4

- SD、SDIO、またはeMMCに構成可能な1ポートのホストコントローラー

- SDクロック周波数は最大50MHz

- SD Host Controller Standard Specification 3.0をサポート

- SDIO card specification 3.0をサポート

- SD Memory Card Specification 3.0をサポート

- SD Memory Card Security Specification 1.01をサポート

- eMMC Specification 4.41をサポート

USB 2.0ホストコントローラーの特徴

USB 2.0デバイスコントローラーの特徴

SD/SDIO/eMMCコントローラーの特徴

I²Cマスターコントローラー

- 2ワイヤーのI²Cシリアルバスインターフェース

- 2つのI²Cスピードをサポート:データレートは標準(100Kbit/s)および高速(400Kbit/s)に対応

- 完全に非同期なI²Cクロック信号

- マスターとしてのI²C動作

GPIOの特徴

- 16本のGPIOピンを備える

- 6本のGPIOピンはS3ステートでもアクティブであり、サスペンド状態からシステムをレジュームさせるために使用できる。

- 残りの10本のGPIOピンはS0ステートにおいてのみアクティブであり、S3ステートでは利用できない。

SPIマスターコントローラー

- 2つのSPIマスターコントローラー

- マスターコントローラーあたり1つのチップを選択

- SCLK周波数は1kHzから25MHzまでの間で設定可能

DMAが可能な高速UARTコントローラー

- 2つの16550準拠のUARTコントローラー

- サポートするボーレートは300から2764800

- ハードウェアフローコントロールが可能な統合されたDMA

レガシーブリッジ

レガシーブリッジはIntelアーキテクチャ互換プラットフォーム(IBM PC互換)を実現するために必要となるハードウェアブロックのコレクションです。キーとなる機能のいくつかがあります:

- フラッシュメモリ専用の20MHz Serial Peripheral Interface (SPI) – ブートファームウェアとシステム構成データ格納用

- SoCに搭載された多数のパワーマネージメント機能を制御するパワーマネージメントコントローラー(PMC)

- レガシーブリッジコンポーネント – レガシーPCプラットフォームとして必須の機能を提供する。レガシーブリッジのコンポーネントには、RTC、割り込みコントローラー、タイマーおよび汎用I/O(GPIO)が含まれる。

提供されるSKU

2013年12月1日現在、以下のSKUが公開されています※5:

| Stepping | SKU | Identifier | ECC | Secure Boot |

MM # | SPEC Code |

|---|---|---|---|---|---|---|

| A0 | 2 | Intel® Quark SoC X1000(16K Cache, 400MHz) | Y | Y | 929172 | ES |

| A0 | 2 | Intel® Quark SoC X1000(16K Cache, 400MHz) | Y | Y | 930236 | SS |

| A0 | 4 | Intel® Quark SoC X1000(16K Cache, 400MHz) | N | N | 929184 | ES |

| A0 | 4 | Intel® Quark SoC X1000(16K Cache, 400MHz) | N | N | 930237 | SS |

| A0 | 5 | Intel® Quark SoC X1000(16K Cache, 400MHz) | Y | N | 929518 | ES |

| A0 | 5 | Intel® Quark SoC X1000(16K Cache, 400MHz) | Y | N | 930239 | SS |

パッケージ

SoCはフリップチップBall Grid Array(FCBGA)パッケージで、393個のソルダーボールを0.593ミリメートルのボールピッチで配置しています。パッケージ寸法は15ミリメートル×15ミリメートルです。

温度関連

- TDP = 1.9W ~ 2.2W(VRに依存)

- 動作温度 = 0 ~ 70℃(一般用)

さらに広い温度に対応するものは近いうちに登場予定

I/Oレベル

チップ標準のI/Oレベルは3.3ボルト(CMOS3.3)です。このためGalileoが5Vをジャンパ切り替えでサポートしているのは、ボード上にレベルシフト機能を搭載することで対応しているのだろうと思います。

まとめ

このように、このSoCは現在のIntelアーキテクチャとよばれるIBM PC互換機能を含めて持っており、ないのはビデオアダプターくらいです。それも必要であれば2本あるPCIeのどちらかにつければ実現できます。このようなことを考えると、超コンパクトなIBM PC互換機を作るのにも使えそうです。

ところで、なぜレガシーブリッジがあるかというと「既存のソフトウェア資産を活かす」というIntelアーキテクチャの命題と正統性がそこにあるからです。レガシーブリッジがなければWindowsやLinuxをはじめとする各種OSコアをそのまま動作させることができなくなります。そうならないように搭載し続ける必要があるわけです。

また、セキュアおよび堅牢であることにも思った以上に機能を割いているように思いました。オンダイのブートROMを搭載していることにより、不正なファームウェアの侵入を防ぐことができますし、メモリへのECCへの対応と、厳しい環境に耐えることが要求されるような用途、例えば電気メーターとかガスメーターなどの分野にも応用ができそうです。

レガシーブリッジとPCI Express(PCIe)のほかに、ARMが標準化した仕様のAMBA Fabricが含まれているのが従来のIntelの設計とは異なる点です。Intel AtomではAMBAではなく独自仕様「IOSF」を採用していました。

全体的には今までのIntelらしくない、面白いチップだなぁ、と仕様を眺めていて思いました。あるいは、大昔、まだIntel 8088がIBM PCに採用されるという大ヒットを出す前のIntelの製品の雰囲気があるような気もします。

2013年12月1日

- SKUによって搭載される機能と搭載されない機能が判明したのでそれを反映しました。

- SKUのリストを追加しました。

- エラッタで機能しないEthernetの機能について脚注を追加しました。

- BSPが公開されたため、Intel Galileo Boardでファームウェアが変更できない可能性への言及を削除しました。

情報とロゴ、図の出典および引用元

- 「Intel Quark SoC X1000 Datasheet(Document Number 329676-001US)」

Intel Makers Community : Intel Quark SoC Documentsよりダウンロード可能

関連記事

- Intel Galileo(Fab D)とKips Bay Fab Cとの違い

- Intel Quark関連コードネームまとめ

- Intel Galileo BoardやKips Bayのファームウェア更新について

- Intel Quark Core(Lakemont Core)はPentiumベースではない

- 2013年12月中旬よりIntel Galileo Board国内販売開始

- Intel Galileo BoardとQuarkに関するまとめ(勝手にFAQ)

- Intel Quark Core自体の仕様(コードネームはLakemont Core?)

- Intel Quark SoC X1000搭載Intel Galileo Boardを発表

- Intel Quarkの正体は80386?それともPentium?

- このアウトオブオーダーはプロセッサコアのアウトオブオーダーとは別なので混同してはならない。

- 要するにSoCに書き込まれたブートROMがファームウェアを認証することが可能となるため、不当なファームウェアを排除することができる。なお、この機能が有効となるのはSecure Bootを有効にしたSKUのIntel Quark SoC X1000に限られる。そうではないSKUではSPI Flashから直接起動する。

- エラッタ85384によるとこの機能はA0ステッピングでは動作しない。今後のステッピングチェンジで修正予定。A0ステッピングでこの機能が必要な場合にはソフトウェア実装で回避が必要。

- SoCがUSBデバイスとして動作するためのデバイスポート

- この表にはSKUの3が抜けている。もし存在するとなると、可能な組み合わせのバリエーションとしてECC:N、Secure Boot:Yが考えられる。