はじめに

前回の「Intel Edison Compute ModuleのMicrocontroller Unit(MCU)を分析する」では、MCUがどのような素性のチップであるかを中心に分析を行いました。今回は、前回の分析では不明のままとなっていたキャッシュ・メモリーについて分析を行ってみたいと思います。

分析の方法

キャッシュの制御情報を得るために特権命令を使用する方法が使えない※1ことやCPUID命令から情報を得る方法ではキャッシュの情報が得られないこと※2から、実際にメモリーを読み出す速度をサイズ別に行い、その傾向を見ることにしました。これによって速度が変化するサイズを探し、その差異が出ている部分があれば、そのサイズを元にキャッシュが効いていると見ることができる範囲を探るという手法です。

今回は以下の条件で計測を行いました:

-

1 KByte刻みで1~96 KByteまでのサイズで計測

計測対象を96 KByteまでにしているのは、MCU SDKのアプリケーションで使用できるメモリー量は120 KBytesまでに制限されているため、プログラム本体で使用する容量、各種変数で使用する容量、スタックで使用する容量などの消費量を勘案して96 KByteとしています。

-

RDTSC命令でプロセッサーの実行サイクルを取得する方法を選択MCU SDKが提供するタイマーにはあまり細かいものがない(最小でμ秒単位)であることや、APIの呼び出しで発生するオーバー・ヘッドを低減させたいこと、またプログラムの単純化などを狙えることから

RDTSC命令の使用を選択しました。また、この命令は初代Pentium(コードネーム「P5」)から導入されたものであり、MCUでも正常に使用できることを確認したかったという意図もあります。 -

読み出しには3種類のサイズ(

BYTE: 8-bit、WORD: 16-bit、DWORD: 32-bit)のREPプリフィクス命令付きのLODS命令を使用読み出しのサイズとして3種を選択したのは、MCUが外部の回路との接続でアクセス単位に応じた方式を選択している可能性を確認できるのではないか、という想定によるものです。また、C言語による読み出し記述ではなく、インライン・アセンブリ言語による

REPプリフィクス命令付きのLODS命令を使用しているのは、メモリーからの読み出し中に極力キャッシュを乱さないようにしたいという意図によるものです。 -

各サイズでの読み出しを100回行い、最もよかった(最も実行クロックが少なかった)値を採用

100回の計測をしているのは割り込みなどの外的要因によって使用するサイクルが増加する影響を避けるためです。その計測した結果のうち最小の値(最良の値)を採用しているのは、割り込みなどの外的要因による値を排除した本来得られるであろうと想定される値を得るためのものです。MCUはWind RiverのViper OS(RTOS)が稼働していて、これはプロテクト・モードで動作しており、アプリケーション・プログラムが割り込みを禁止する

CLI命令の実行を許可していないことによります。

計測結果

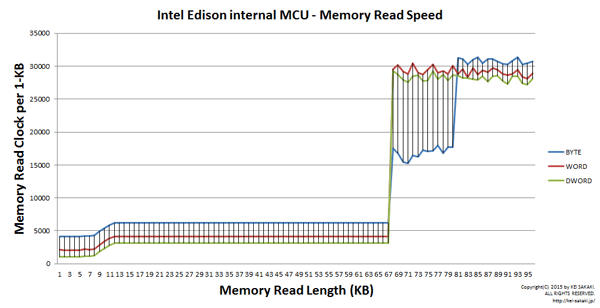

実際にMCU上で計測を行い、1 KByte単位で何クロックかかっているかを計算し、その結果をサイズ別にグラフにしたものを以下に示します:

分析

このサイズごとの計測結果には5つの傾向があるように見えます:

- 最小のクロックでアクセスが可能なサイズ(1~8 KByte)

- 後続の安定的なクロックでアクセス可能な領域へ続く、順次的に必要クロック数増加するサイズ(9~12 KByte)

- 最小のクロックではないものの、安定的なクロック数でアクセスすることができるサイズ(12~67 KByte)

- 安定していたクロック数が突如増加するサイズ(68~80 KByte)

- さらにクロック数が増加するサイズ(81~96 KByte)

最小のクロックでアクセスできるメモリー・サイズは8 KByteまでであることが見て取れます。この後、アクセス対象のメモリー・サイズが増えていく9 KByteから12 Kbyteまでの間は緩やかに必要なクロックが増加していきます。

12 KByteから67 KByteまでのサイズは安定的です。ここまでのアクセス速度を見る限り、Intel Edison Compute Moduleに内蔵されたMCUからアクセス可能なSRAM(192 KByte)のアクセス速度が素直に反映されているものとみることができそうです。

68 KByteから80 KByteまでの領域は突如としてアクセスに必要なクロック数が増加するとともに、クロックが安定しなくなります。

81 KByte以降はさらにアクセスに必要なクロック数が倍増します。

考察

以上の分析を踏まえて、考察してみます:

- 最小のクロックでアクセスが可能な8 KByteまでのサイズはキャッシュが効いていると想定される。

- 9 KByteから12 KByteまでのサイズではアクセスに必要なクロック数が増えていく。サイズの増加によって順次必要クロック数が増えていくのはキャッシュからあふれていく部分が増えていくことによるものだと考えられる。

- その後の68 KByteまでの安定したアクセス速度がIntel Edisonに内蔵されたMCUからアクセスすることができるSRAMの速度であると考えられる。

68 KByteから80 KByteまでの必要クロック数が急激に増加する理由、および81 KByte以降でさらに必要クロック数が倍増する明確な理由は正直なところよくわかりません。しかし、いくつか可能性を考えることができます:

-

アクセス時間が増加することにより、割り込み制御などのWind River Viper OS側処理のクロックが入ってしまっている。

しかし、もしも割り込みが原因であれば特定のメモリー・サイズで現象が発生するのではなく、特定のアクセス時間に一致する形で現象が現れるはずです。というのも、MCUは何らかの割り込み源から時間を測定するための割り込みを得ていると考えるのが妥当性が高いからです。MCU SDKで提供されるAPIにも時間制御によるものが存在していることからも、これは明らかだと言えるでしょう。※3

-

実はキャッシュが67 KByteまで効いている。

これも考えにくいように思います。8 KByteまでが最も速いことを考え合わせると、1次キャッシュがあり、その後2次キャッシュがある、というような構成まで考える必要が出てきます。※4そこまで大規模なものを載せているとはちょっと考えにくいと思うのです。また、なだらかにクロック数が増加するのではなく、急激に増加していることからキャッシュの可能性は低いと考えられます。

-

メモリーへアクセスするためのバンクが異なっている部分が含まれ、アクセス速度が安定しなくなっている。

バンク跨ぎについては現状で公開されている資料にはその手の記述は何もなくなんとも言えません。あくまでその可能性がありえることを指摘することしかできません。

まとめ

以前に書いた「Intel Edisonに搭載されているMCUは本当にQuark?」において、MCUにはキャッシュが存在しない可能性を考察しましたが、今回得られた結果によれば、8 KByteのキャッシュが存在していると考えることが合理的です。

MCUの設計がベースとしていると思われる「Write-back Enhanced Intel DX4(コードネーム「P24C」)」のキャッシュが16 KByteであることを考えると、その半分しか存在しないと思われるキャッシュの容量はやや不自然です。しかし、一方で「Write-back Enhanced Intel DX2(コードネーム「P24D」)」という、キャッシュが8 KByteの製品があったことも考え合わせれば決して不自然とは言えません。

おそらく、Write-back Enhanced Intel DX4と同DX2の論理設計は同じで、オプションでキャッシュ・サイズを8 KByteと16 KByteを選択できるようになっているのでしょう。さらに、Write-back Enhanced Intel DX4および同DX2は浮動小数点プロセッサー(FPU)を内蔵していましたが、MCUは内蔵していません。FPUもオプションで有りと無しを選択できるのでしょう。このほかには、Write-back Enhancedはオプションで構成できると読める記述がIntel Quark Core(コードネーム「Lakemont Core」)の開発者向けのドキュメント「Intel® Quark Core Hardware Reference Manual」にあります。

これらをまとめると、Intelが保有している486シリーズ系の設計は以下のオプションがあるようです:

- キャッシュ・サイズを8 KByteと16 KByteで選択できる。

- 浮動小数点プロセッサー(FPU)のありとなしを選択できる。

- Write-back Enhancedのありとなしを選択できる。

2015年6月7日 19時追記

当初掲載していたグラフ(下図)の差し替えを行いました:

比較するとわかりますが、68~80 KByteの部分が異なります。当初はBYTEだけが階段状になっていましたが、おかしな形状であったため、掲載後にも追試を繰り返していたところ、同様の傾向のデータがWORDとDWORDでも出ることがあることがわかりました。と同時に、逆にBYTEでも階段状にならないことがあることが分かりました。

今回の測定方針では「最もよかった(最も実行クロックが少なかった)値を採用」としていますので、階段状のデータが取れたものを採用してグラフを差し交えるとともに、関連する個所の文章を調整しました。

- MCUはWind River Viper OS(RTOS)が動作しており、この上でMCU用のアプリケーション・プログラムを実行する構造となっています。アプリケーションはOSの動作に影響を与える可能性のある命令の使用が制限されています。

CPUIDにはキャッシュの情報を引き渡す部分があるのですが、MCUはこの情報が空になっています。詳しくは前回の「Intel Edison Compute ModuleのMicrocontroller Unit(MCU)を分析する」を参照ください。- ただし、アプリケーション・プログラムから自由に使用できるプログラマブル・タイマー割り込みは現在のところ存在していません。

- 仮に想定するとなると、1次キャッシュが8 KByteで2次キャッシュが64 KByteのような感じになるのでしょうか?