はじめに

Intel Corporationが送り出したIntel Edison Compute Moduleは、非常にコンパクトで各種用途に比較的簡単に応用できることから、多くの活用例が発表されています。このIntel Edison Compute Moduleを使用するために必須のドキュメントが「Intel® Edison Compute Module Hardware Guide / 331189-004」です。

このドキュメントはかなり詳細な内容が含まれてはいるのですが、現時点では英語版しか存在していません。そこで、今回は私の視点、私の理解で読んだ内容を元に日本語で書き起こした同ドキュメントを「Intel® Edison Compute Module / ハードウェア・ガイド」として公開してみることにします。

該当ドキュメントはダウンロード時に特にライセンスの確認がなく、該当ドキュメントの文頭にある宣言文を読む限り、Intelのライセンス上も問題がなさそうだと思われる(転載と翻訳を禁止するとの明示文がない)ため、参考にはなるかと思い公開するものです。

お願い

もしもIntelの関係者で、私がこの日本語ドキュメントを公開することが何らかのライセンスや法的問題があるとお考えであるならば、メールにてご連絡をいただければと思います。その際は、私がメールの送付主がIntel関係者であることを認識できるようにIntel社内からメールを送信し、所属・肩書き等を添えてください。

著作権等

英語版の資料をベースにしているこの日本語ドキュメントはIntelの著作権が及ぶ範囲内にあります。その上で、この日本語ドキュメントには“さかきけい”の著作権が発生しています。“さかきけい”はすべての著作権法上の権利を留保します(詳しくは「ご利用上の注意とお願い」を参照ください)。

免責の表明

この日本語ドキュメントはIntel Corporationが公開している「Intel® Edison Compute Module Hardware Guide / 331189-004」に記載されている情報を元に、“さかきけい”の理解で作成したものです。このためIntel Corporationには何らこの日本語ドキュメントに対する責任はありませんので、この日本語ドキュメントに関連する問い合わせをIntelに対して行うことを禁止します。

また、この日本語ドキュメントを作成した“さかきけい”も何ら責任を負いません。この日本語ドキュメントの内容は、利用者自身の責任においてのみ使用することができます。

使用上の注意

- Intelによる法的な意味合いを持つと考えられる記述は英文のままとしています。これは、日本語にすることで意味合いが変化することを防ぐ目的のものです。しかし、その部分は英語原文に付属する部分であることを前提としなければなりません。したがって、本日本語ドキュメントではなく、文脈としては原書に付属することになります。本日本語ドキュメントにおいては、Intelが免責を宣言する部分はその通りですが、何らかの権利や許可を与える部分についてはすべて無効であるとご理解ください。※1

- 複数の英単語によって構成される語は、単語間に「・」を入れて表現しています。例:ルート・ファイル・システム※2

- 原則として単語末の長音記号「ー」は省略しない方針で編集しています。例:プロセッサー※3

- 気づいたTypoや編集ミスなどは明確であると考えられる場合に若干修正しています。

- 日本語での記述におかしいと思われる個所がある場合には原書をあたってください。

- 技術的などの理由で記載内容にわからない事項がある場合には別途調べてください(“さかきけい”に質問のメールを送るのはご遠慮ください※4)。

- 明らかな誤訳がある場合には具体的なご指摘をメールでお知らせいただけると助かります。

- 記述内容に誤りがある場合にもお知らせいただけると嬉しく思います。ただし、原書も間違っている場合には特に日本語ドキュメントを修正することはせずに、訳注を追加するだけとするかもしれません。

- 前述の内容と被りますが、“さかきけい”は何ら責任や義務を負うものではありません。

文書についてのご指摘をいただける方へのお願い

- なるべく平坦でかつ理解しやすい程度に周辺情報を含む、日本語でのご指摘をお願いします。特に今回は“さかきけい”の理解の範疇を超えたハードウェアに関する部分のため、従来より多くの問題が存在し、それを理解するための周辺情報も多く必要であることが見込まれます。

- “さかきけい”の主観において、いただいた情報の適用を行わないことがあることをあらかじめご理解ください。

- ご連絡をいただける際には、以下の優先度でお願いします:

- “さかきけい”へのメール

- Facebook経由でのコンタクト

- このメモへのコメント

ただし、このメモへのコメントの場合、大量のスパム・コメントに埋もれて反応が遅くなったり気づかない可能性があります。できる限りメールかFacebookでお願いします。

Intel® Edison Compute Module

ハードウェア・ガイド

2015年1月

リビジョン 004

ドキュメント番号: 331189-004

Notice: This document contains information on products in the design phase of development. The information here is subject to change without notice. Do not finalize a design with this information.

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL’S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

A “Mission Critical Application” is any application in which failure of the Intel Product could result, directly or indirectly, in personal injury or death. SHOULD YOU PURCHASE OR USE INTEL’S PRODUCTS FOR ANY SUCH MISSION CRITICAL APPLICATION, YOU SHALL INDEMNIFY AND HOLD INTEL AND ITS SUBSIDIARIES, SUBCONTRACTORS AND AFFILIATES, AND THE DIRECTORS, OFFICERS, AND EMPLOYEES OF EACH, HARMLESS AGAINST ALL CLAIMS COSTS, DAMAGES, AND EXPENSES AND REASONABLE ATTORNEYS’ FEES ARISING OUT OF, DIRECTLY OR INDIRECTLY, ANY CLAIM OF PRODUCT LIABILITY, PERSONAL INJURY, OR DEATH ARISING IN ANY WAY OUT OF SUCH MISSION CRITICAL APPLICATION, WHETHER OR NOT INTEL OR ITS SUBCONTRACTOR WAS NEGLIGENT IN THE DESIGN, MANUFACTURE, OR WARNING OF THE INTEL PRODUCT OR ANY OF ITS PARTS.

Intel may make changes to specifications and product descriptions at any time, without notice. Designers must not rely on the absence or characteristics of any features or instructions marked “reserved” or “undefined.” Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them. The information here is subject to change without notice. Do not finalize a design with this information.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication, or disclosure is subject to restrictions stated in Intel’s Software License Agreement, or in the case of software delivered to the government, in accordance with the software license agreement as defined in FAR 52.227-7013.

The products described in this document may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

The code names presented in this document are only for use by Intel to identify products, technologies, or services in development that have not been made commercially available to the public, i.e., announced, launched, or shipped. They are not “commercial” names for products or services and are not intended to function as trademarks.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel’s website at http://www.intel.com/design/literature.htm.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See http://www.intel.com/products/processor_number for details.

Intel, the Intel logo, and Intel Atom are trademarks of Intel Corporation in the United States and other countries.

* Other brands and names may be claimed as the property of others.

Copyright © 2015 Intel Corporation. All rights reserved.

コンテンツ

- 1 はじめに

- 2 高レベル機能の説明

- 3 コンポーネントとサブシステムの詳細

- 4 外部インターフェース・ピンと電気特性

- 5 Intel® Edisonへの電力供給

- 6 Intel® Edison物理仕様

- 7 レイアウト

- 8 取り扱い

図一覧

- 図1 Intel® Edisonブロック・ダイアグラム

- 図2 上から見たIntel® Edison Compute Module

- 図3 下から見たIntel® Edison Compute Module

- 図4 クロック・ジッターの定義

- 図5 周期ジッターの測定方法

- 図6 I2Cバス上のスタンダード/ファスト・モードのデバイスのタイミング定義

- 図7 I2Cバスでハイ・スピードモード用デバイスのタイミングの定義

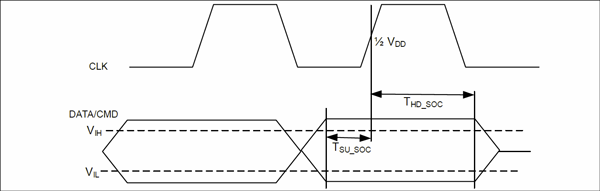

- 図8 SD/SDIO タイミング・ダイアグラム (DDR50)

- 図9 SD/SDIO 出力タイミング・ダイアグラム (SDR 12/25)

- 図10 SD/SDIO 入力タイミング・ダイアグラム (SDR12/25)

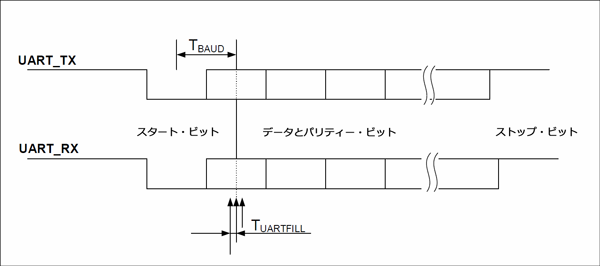

- 図11 UARTタイミング・ダイアグラム

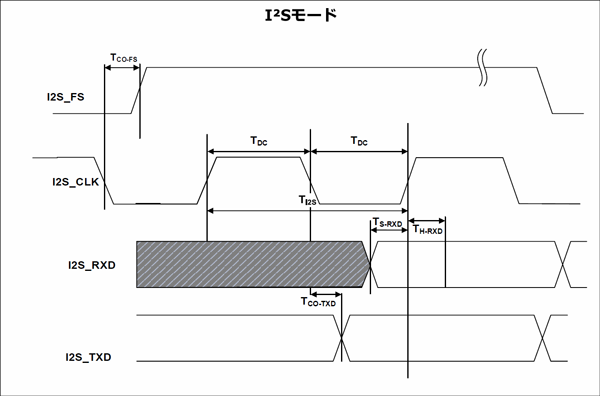

- 図12 I2SモードにおおけるI2Sマスター・ポートのタイミング

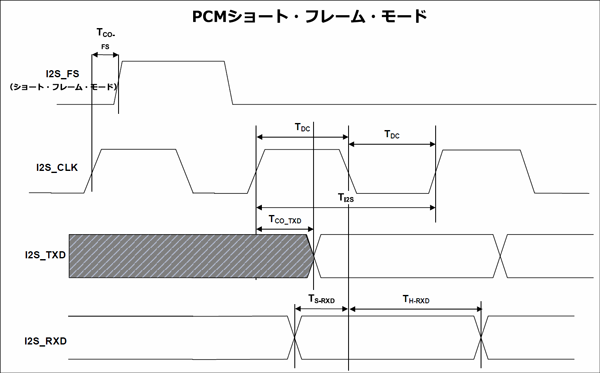

- 図13 PCMショート・フレーム・モードにおけるI2Sマスター・ポートのタイミング

- 図14 PCMロング・フレーム・モードにおけるI2Sマスター・ポートのタイミング

- 図15 I2SモードにおけるI2Sスレーブ・ポート・タイミング・パラメーター

- 図16 PCMショート・フレーム・モードにおけるI2Sスレーブ・ポート・タイミング・パラメーター

- 図17 PCMロング・フレーム・モードにおけるI2Sスレーブ・ポート・タイミング・パラメーター

- 図18 SPIマスター・タイミング

- 図19 SPIスレーブ・タイミング

- 図20 GPIOバッファー入力範囲

- 図21 Intel® Edison用の外部USB設計の例

- 図22 Intel® Edisonとリチウムポリマー・バッテリーの直接接続の例

- 図23 Intel® EdisonにFETによる隔離を備えたリチウムポリマー・バッテリーの例

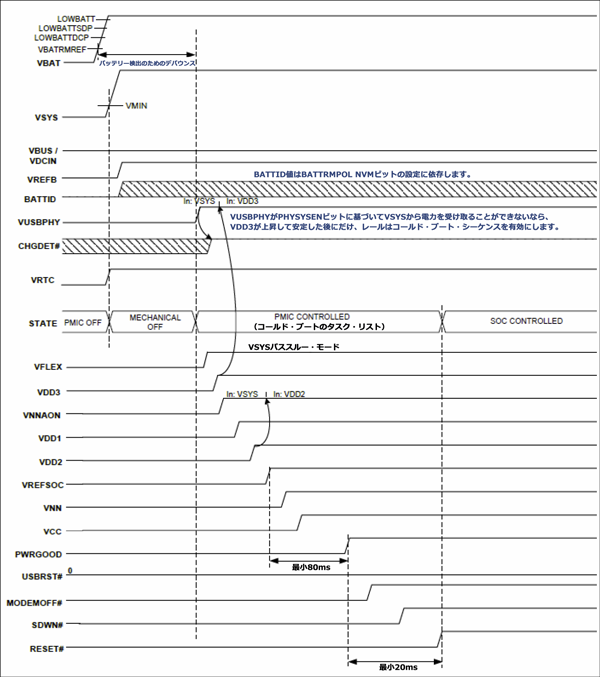

- 図24 Intel® Edisonのコールド・ブート・シーケンス

- 図25 Intel® Edisonモジュールの物理寸法(PCBを上から見下ろした図)

- 図26 アンテナ周辺領域

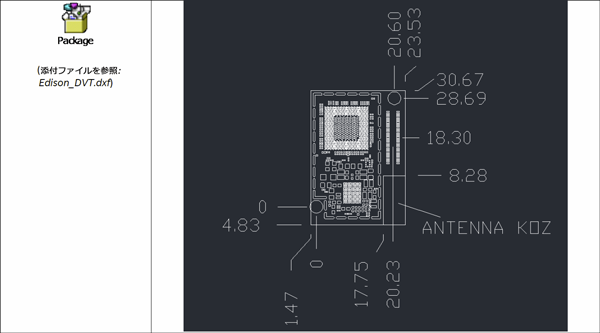

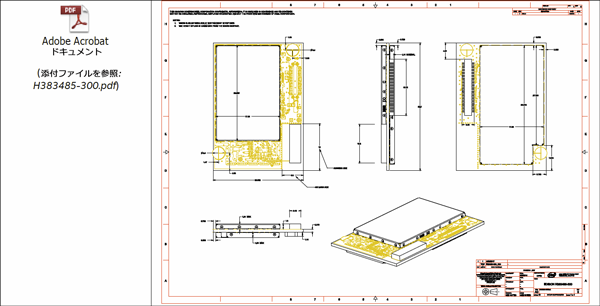

- 図27 DXFによるレイアウト

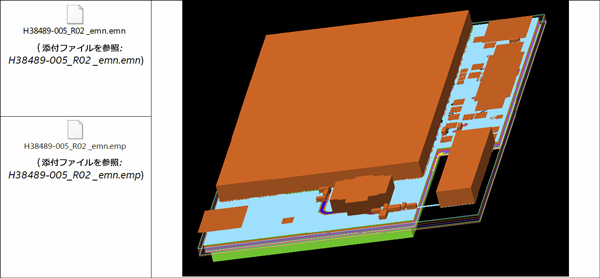

- 図28 PTC ENM画像

- 図29 H383485-300

- 図30 Intel® Edisonモジュールの挿入

表一覧

- 表1 製品固有ドキュメント

- 表2 ハードウェアの特徴

- 表3 Intel® Edison 70ピン・コネクター・パーツ番号

- 表4 Intel® Edison 70ピン・コネクターのボード間結合の高さ

- 表5 Intel® Edisonコネクターのピンアウトよび信号リスト

- 表6 19.2 MHz OSC_Clock 出力

- 表7 RTCクロック入力仕様

- 表8 スタンダード/ファスト・モードI2Cバス用デバイスのためのAC仕様

- 表9 I2Cスタンダード/ファスト・モードにおけるSCLとSDAに対するプルアップ強度の設定

- 表10 I2Cスタンダード/ファスト・モードのデバイスのDC仕様

- 表11 ハイ・スピード・モードI2Cバス用デバイスのためのAC仕様

- 表12 I2Cハイ・スピード・モードにおけるSDAに対するプルアップ強度の設定

- 表13 I2Cハイ・スピード・モードにおけるSCLに対するプルアップ強度の設定

- 表14 ハイスピード・モードのI2Cバス・デバイス用DC仕様

- 表15 SD AC仕様

- 表16 SD/SDIO DC仕様

- 表17 UART AC仕様

- 表18 Intel® Edison I2S 使用可能なフォーマット

- 表19 I2Sポート概要(リファレンス・デザインによる実装)

- 表20 I2SマスターACタイミング

- 表21 I2Sスレーブ・モードACタイミング・パラメーター

- 表22 I2SバッファーDC仕様

- 表23 SPIポートの概要

- 表24 SPIモード

- 表25 SPIマスターACタイミング

- 表26 SPIスレーブACタイミング

- 表27 GPIOバッファーAC仕様

- 表28 GPIOバッファーDC仕様

- 表29 GPIOプルアップおよびプルダウン仕様

- 表30 Intel® Edison PWM設定の例

- 表31 BBCHGRCFG – バッテリー・バックアップ充電器およびメイン・バッテリー充電器IC構成レジスター

- 表32 ESD 性能

- 表33 SDカードのレイアウト

改定履歴

| リビジョン | 詳細 | 日付 |

|---|---|---|

| ww32 | 初期リリース | 2014年8月4日 |

| ww34 | 若干の編集 | 2014年8月20日 |

| 001 | 最初の一般公開 | 2014年9月9日 |

| 002 | 若干の修正 | 2014年9月16日 |

| 003 | 「ソフトウェア・リカバリー・モード」セクションの追加 | 2014年11月14日 |

| 004 | 4章に多くの内容を追加 | 2015年1月30日 |

1 はじめに

このドキュメントはIntel® Edison Compute Moduleのハードウェア・インターフェースについて説明するものです。これは、どのようにIntel® Edison Compute Moduleと直接接続する拡張ボードを作成すべきなのかという概要について情報を提供するものです。

1.1 参照

表1 製品固有ドキュメント

| 参照 | 名称 | 番号/場所 |

|---|---|---|

| 331188 | Intel® Edison Board Support Package User Guide | |

| 331189 | Intel® Edison Compute Module Hardware Guide | (このドキュメント) |

| 331190 | Intel® Edison Breakout Board Hardware Guide | |

| 331191 | Intel® Edison Kit for Arduino* Hardware Guide | |

| 329686 | Intel® Galileo and Intel® Edison Release Notes | |

| [GSG] | Intel® Edison Getting Started Guide | W: http://www.intel.com/support/edison/sb/CS-035336.htm M: http://www.intel.com/support/edison/sb/CS-035344.htm L: http://www.intel.com/support/edison/sb/CS-035335.htm |

| 331438 | Intel® Edison Wi-Fi Guide | |

| 331704 | Intel® Edison Bluetooth* Guide |

2 高レベル機能の説明

Intel® Edison Compute Moduleは、IoTとウェアラブル・コンピューティング製品の試作および製造に対する障壁をさげ、誰もがデザインを行えるようにするための製品です。Intel® Edisonは、コアとなる処理システムと接続性を確保する要素を搭載しています: プロセッサーとプロセッサー・パワー・マネージメントIC、RAM、eMMC、そしてWi-Fi/BT。Intel® Edisonは、70ピンのコネクターを経由してエンド・ユーザーのシステムと接続するモジュールです。Intel® Edisonは、電源入力、およびバッテリー電源式システムのためのバッテリー再充電のように総合的なシステム電源を提供することをエンド・ユーザーに委ねています。表2に主要なシステム・コンポーネントを示します。

表2 ハードウェアの特徴

| コンポーネント | 内容 |

|---|---|

| プロセッサー | デュアルコア、デュアルスレッドのIntel® Atom™ CPU 500 MHzと32ビットIntel® Quark™マイクロコントローラー 100 MHzを22 nm Intel® SoCに集積 |

| RAM | 1 GB LPDDR3 POP メモリー (2 チャネル 32 ビット 800 MT/sec) |

| 内蔵ストレージ | 4 GB eMMC (v4.51 仕様) |

| 電源 | TI SNB9024 電源制御 IC |

| 無線 | デュアル・バンド (2.4 および 5 GHz) IEEE 802.11a/b/g/n |

| Bluetooth* | BT 4.0 + 2.1 EDR |

| アンテナ | オンボードのデュアル・バンド対応チップ・アンテナ、または外部アンテナのためのu.FL |

| コネクター | 70ピン ヒロセ電機 DF40シリーズ(スタック高1.5、2.0、または3.0mm) |

| サイズ | 最大 35.5 × 25.0 × 3.9 mm(確認済み) |

| 電源入力 | 3.15~ 4.5 V |

| I/O | 40の汎用GPIOを以下の中から構成することができる:

|

| USB 2.0 | OTG対応の1コントローラー |

| クロック出力 | 19.2 MHz, 32 kHz |

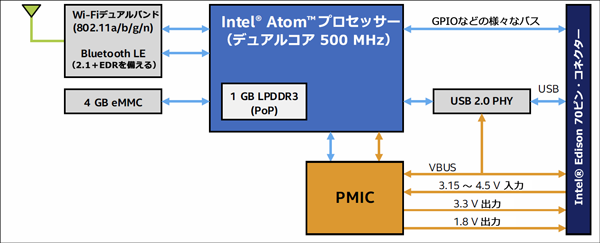

2.1 ブロック・ダイアグラム

基本的なIntel® Edisonのブロック・ダイアグラムを図1に示します。

図1 Intel® Edisonブロック・ダイアグラム

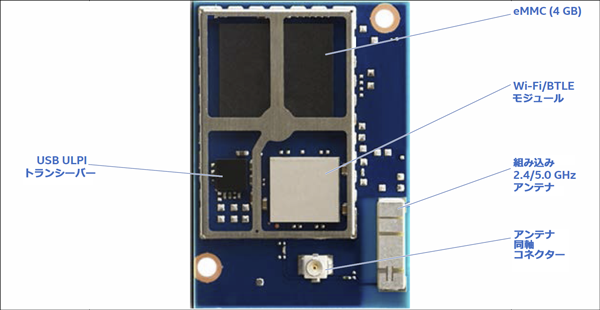

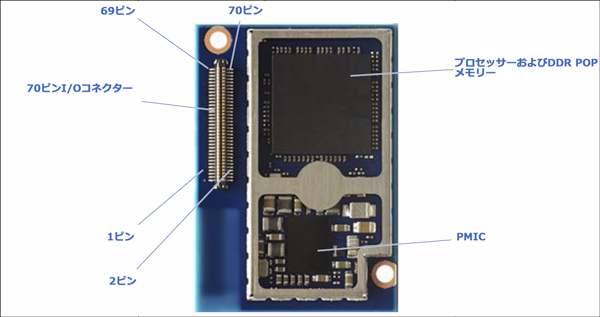

2.2 モジュールの写真

図2 上から見たIntel® Edison Compute Module

図3 下から見たIntel® Edison Compute Module

3 コンポーネントとサブシステムの詳細

3.1 Intel® Atom™ プロセッサー

Intel® Edisonは先進性のあるIntel® Atom™ プロセッサーを採用し、スマートフォン市場に向けた22nm System-on-Chipです。SoCは500 MHzで動作する2つのIA-32コアを搭載しています。2つのCPUコアで1MBのキャッシュを共有し、2ワイド・インストラクション・デコードとアウト・オブ・オーダー実行が可能なアーキテクチャーを備えます。これには、Intel SIMD Extensions 2、3、4(SSE2、SSE3、SSE4.1/4.2)が含まれます。

3.2 Wi-Fi / BTモジュール

村田製作所の統合Wi-Fi BTモジュールはBroadcom BCM43340 Wi-Fi / BTデバイスを使用しています。

Broadcom BCM43340は1つのチップで4デバイスを供給する、高レベルに統合されたモバイルまたはハンドヘルド用の無線システムで、デュアル・バンド(2.4 / 5 GHz)IEEE 802.11a/b/g/nのMAC/ベースバンド/無線通信とBluetooth 4.0に対応しています。

- デュアルバンド 2.4 GHzおよび5 GHz IEEE 802.11 a/b/g/n

- 20 MHzおよび40 MHzのチャネルに対応するPHYレイヤーにより、最大で150 Mbps、上位レイヤーのスループットで90 Mbpsを超える、シングルストリームIEEE 802.11nをサポート

- 標準SDIO v2.0とgSPI(48 MHz)ホスト・インターフェースをサポート

- Bluetooth* Core Specification Version 4.0準拠で、将来の仕様をサポートする余地を持つ

- セキュリティー:

- 高度な暗号化と認証が可能なWPAおよびWPA2(Personal)をサポート

- 高速なデータ暗号化とIEEE 802.11iとの互換性のためのAES対応の無線LANハードウェア

- リファレンス無線LANサブシステムは、Cisco互換拡張(CCX、CCX 2.0、CCX 3.0、CCX 4.0、CCX 5.0)を提供※5

- リファレンス無線LANサブシステムは、Wi-Fi protected setup(WPS)を提供

3.3 管理されたNAND(eMMC)フラッシュ

Intel® Edisonは、ファイル・システムとユーザー・データを保存する管理されたNANDを4 GB搭載しています。管理されたNANDフラッシュには、フルMMCコントローラー、ウェアレベリング・ファームウェア、および典型的なMMCカードの各種機能がスモールBGAフォームファクターであることを除いてすべて含まれます。

- バス・モード

- データ・バスの幅:1ビット(デフォルト)、4ビット、8ビット

- データ転送レート:最大200 MBps(HS200)

- MMC I/Fクロック周波数:0~200 MHz

- MMC I/Fブート周波数:0~52 MHz

3.4 DDR SDRAM

Intel® Edisonは最大速度1033 MT/sの1 GB LPDDR3メモリーをサポートします。

- 8バンク

- 行アドレス R0~R13

- 列アドレス C0~C9

- デュアルチャネル 32ビット

- 最大クロック 400 MHz(800 MT/s)

3.5 パワー・マネージメントIC(PMIC)

Intel® EdisonはTexas Instruments* SNB9024 Power Management Integrated Circuit (PMIC)を使用しています。SNB9024 PMICはシステム・ボードの面積を最小化することが要求される、高機能統合が必要なモバイル・アプリケーション・プロセッサー・プラットフォームに適しています。(これは)電圧制御、A/D変換、GPIOおよびRTCをサブシステムに含んでいます。SNB9024デバイスは制御と設定にI2Cインターフェースを使用しています。システム・コントロール用の信号だけではなく、コア電圧レールの設定を行うために、SOCとPMICの間にシリアル・ボルテージIDインターフェースも存在しています。

- 4つの高効率なバック・コンバーター(降圧コンバーター)

- 2つのデュアルフェーズ 0.55 ~ 1.2 V @ 4.8 A ダイナミック電圧スケーリング(DVS)を併用

- 1つのデュアルフェーズ 1.24 V @ 2.5A

- 1つのシングルフェーズ 1.8 V @ 1.1A

- 1つの5 V 1.2A ブースト・コンバーター(昇圧コンバーター)

- 1つの3.3 V/3.4 V 1.4 A バックブースト・コンバーター(負圧コンバーター)

- 5つのロー・ドロップアウト・レギュレーター(低損失レギュレーター)

- 3つのプログラマブル 1.05~2.85 V @ 100~300 mA

- 1つの高精度 1 V @ 2mA

- 1つのダイナミック電圧スケーリング(DVS) 0.75~0.95 V @ 220mA

- スルー・レート制御および外部のロード・スイッチ制御を用いた2つのロード・スイッチ

- USBおよびAC/DCアダプター電源装置の検出と外部の充電制御(有効/無効および電流制限)

- I2Cインターフェースと専用のSVI

- PMICイベント用の割り込み制御

- 7つの汎用 1.8 V I/Oと、それらのうち2つに対する最大3.3 Vのサポート

- バックアップ・タイマーのための32.768 kHz RTC

- アラーム・タイマーの割り込み

- スリープ・クロックの出力(32.768 kHz)

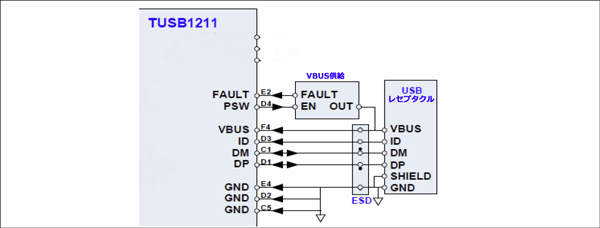

3.6 USB 2.0 トランシーバーULPIインターフェース

TUSB1211はUSB 2.0トランシーバー・チップで、ULPIインターフェース経由でUSBコントローラーに接続されるようにデザインされています。(これは)すべてのUSB 2.0データ・レート(ハイスピード 480 Mbps, フルスピード 12 Mbps および ロースピード 1.5 Mbps)およびホストとペリフェラル・モードの両方をサポートしています。TUSB1211は、ホスト・ネゴシエーション・プロトコル(HNP : Host Negotiation Protocol)およびセッション・リクエスト・プロトコル(SRP : Session Request Protocol)を含む、USB 2.0仕様にOTG(Ver 1.3)でオプショナルとして追加された仕様をサポートします。

TUSB1211はUSB Battery Charging Specification v1.1(USBバッテリー充電仕様 v1.1)をサポートし、DP/DMラインにおける制御とセンシングのための充電器検出モジュールと、IDラインにおける制御とACA (Adaptive Charger Accessory : 適応型充電器アクセサリー)の検出を統合しています。ACAはポータブルOTGデバイスに対し、USB充電器または充電ダウンストリーム・ポートとアクセサリーの同時接続を許容します。構成ビットが許容するACA-アグノスティック・レガシー・リンク※6は、ACAを通じて接続したアクセサリー・ポートから正しく通信を行います。

3.7 統合チップ・アンテナまたは外部アンテナ用のu.FLコネクター

Intel® Edisonモジュールは、統合されたデュアルバンド 2.4/5 GHzアンテナをオンボードに搭載しています。搭載されたアンテナは、主にスモール・フォーム・ファクターのプラスチック・デバイスで使用します。より大きなデバイスあるいは金属エンクロージャーを装備する機器のために、別バージョンのIntel® Edisonは外部アンテナを接続するための業界標準u.FLコネクターを利用可能です。これにより、エンド・ユーザーが最適な性能のためのアンテナを決定することができるようになります。

注記: アンテナ内蔵バージョンのボードにもu.FLコネクターが存在していますが、これは製造試験で使用するためだけのものです。内蔵アンテナがあるボードでは外部アンテナを接続しないでください。

3.8 70ピン・インターフェース・コネクター

70ピン・コネクターを通してエンド・ユーザーのデバイスとIntel® Edisonモジュールを接続します。Intel® Edisonのコネクターは、度々「プラグ」コネクターとも呼ばれる、ヒロセ電気 70ピン DF40シリーズ「ヘッダー」コネクターを搭載しています。Intel® Edisonに搭載されている「ヘッダー・コネクター」のヒロセ電機パーツ番号はDF40C-70DP-0.4V(51)です。

拡張ボードとの結合に使用するヒロセ電機コネクターは“レセプタクル(ソケット)”コネクターです。この結合用“レセプタクル”コネクターは3つの異なる高さのものが入手できます。ボード間の結合スタック高は、1.5、2.0または3.0mmです。表3に“レセプタクル”コネクターおよび拡張ボードに対応する、DigiKeyとMouserのパーツ番号とヒロセ電機のパーツ番号を示します。

表3 Intel® Edison 70ピン・コネクター・パーツ番号

| ヒロセ電機パーツ番号 | 結合スタック高 | DigiKeyパーツ番号 | Mouserパーツ番号 |

|---|---|---|---|

| DF40C-70DS-0.4V(51) | 1.5 mm | n/a | 798-DF40C70DS04V51 |

| DF40C(2.0)-70DS-0.4V(51) | 2.0 mm | H11908CT-ND (少量) H11908TR-ND (テープおよびリール) |

798-DF40C2070DS04V51 |

| DF40HC(3.0)-70DS-0.4V(51) | 3.0 mm | n/a | n/a |

Intel® Edison Arduinoボードは、2.0 mmボード間スタック高のコネクターを使用しています。

Intel® Edison Compute Moduleの底面(70ピン・コネクターのある側)は、コンポーネントの高さ(シールドの高さ)が1.5 mmあり、もし、1.5 mmコネクターを使用するのであれば、接続するPCBに対してぴったりくっついての装着となります。表4※7に、Intel® Edisonの下のコンポーネントのための、拡張ボードのコンポーネントの高さ制限を示します。

表4 Intel® Edison 70ピン・コネクターのボード間結合の高さ

| ヒロセ電機パーツ番号 | ボード間結合の高さ | Edisonの下に許容される高さ |

|---|---|---|

| DF40C-70DS-0.4V(51) | 1.5 mm | n/a |

| DF40C(2.0)-70DS-0.4V(51) | 2.0 mm | 0.5 mm |

| DF40HC(3.0)-70DS-0.4V(51) | 3.0 mm | 1.5 mm |

Intel® Edisonは、直径2.0 mmの2つの取り付け用の穴によって拡張ボードに固定します。常に設置埋め合わせ(設置埋め合わせ材: スペーサー)は結合コネクターの高さと一致していなければなりません(1.5、2.0、または3.0 mm)。

表5にIntel® Edison 70ピン・コネクターのピンアウトと信号を示します。

表5 Intel® Edisonコネクターのピンアウトよび信号リスト

| ピン | 信号名 | 別の機能 | 詳細 |

|---|---|---|---|

| 2, 4, 6 | VSYS | システム入力電源 (3.3~4.5 V) | |

| 8, 10 | 3.3 V | システム 3.3 V 出力 | |

| 12 | 1.8 V | システム 1.8 V 出力 (入出力電圧レベルと同じ) | |

| 14 | DCIN | 入力。DC電源アダプターからの給電ならばVSYSと接続する(バッテリーからの給電ならば何も接続しない)。 | |

| 1,5,9,11,13,15 | GND | グラウンド | |

| 7 | MSIC_SLP_CLK3 | 32 kHzのスリープ・クロック出力 | |

| 3 | USB_ID | USB OTG IDピン | |

| 16 | USB_DP | USB D+ | |

| 18 | USB_DN | USB D- | |

| 20 | USB_VBUS | USB VBUS 入力 (システムへの給電ではない) | |

| 17 | PWRBTN# | 電源/スリープ・ボタン・入力 (負論理) | |

| 19 | FAULT | USB電源障害入力 (外部の電流制限スイッチより) | |

| 21 | PSW | USB電源出力有効 (外部の電流制限スイッチへ) | |

| 23 | V_VBAT_BKUP | リアルタイム・クロック(RTC)バックアップ・バッテリー入力 | |

| 36 | RESET_OUT# | システム・リセット出力 (負論理) | |

| 24 | GP44 | GPIO | |

| 25 | GP165 | GPIO | |

| 26 | GP45 | GPIO | |

| 28 | GP46 | GPIO | |

| 30 | GP47 | GPIO | |

| 32 | GP48 | GPIO | |

| 34 | GP49 | GPIO | |

| 42 | GP15 | GPIO | |

| 48 | GP14 | GPIO | |

| 35 | GP12_PWM0 | PWM_0 | GPIO, PWM出力を備える |

| 33 | GP13_PWM1 | PWM_1 | GPIO, PWM出力を備える |

| 37 | GP182_PWM2 | PWM_2 | GPIO, PWM出力を備える |

| 39 | GP183_PWM3 | PWM_3 | GPIO, PWM出力を備える |

| 41 | GP19 | I2C_1_SCL | GPIO, I2C1 クロック (I2Cとして構成されているならオープン・コレクター) |

| 43 | GP20 | I2C_1_SDA | GPIO, I2C1 データ (I2Cとして構成されているならオープン・コレクター) |

| 45 | GP27 | I2C_6_SCL | GPIO, I2C6 クロック (I2Cとして構成されているならオープン・コレクター) |

| 47 | GP28 | I2C_6_SDA | GPIO, I2C6 データ (I2Cとして構成されているならオープン・コレクター) |

| 50 | GP42 | I2S_2_RXD | GPIO, I2S2 データ受信 (入力) |

| 52 | GP40 | I2S_2_CLK | GPIO, I2S2 クロック (出力) |

| 54 | GP41 | I2S_2_FS | GPIO, I2S2 フレーム・シンク (出力) |

| 56 | GP43 | I2S_2_TXD | GPIO, I2S2 データ送信 (出力) |

| 22 | GP134 | UART_2_RX | GPIO, UART2 受信 (入力) |

| 27 | GP135 | UART_2_TX | GPIO, UART2 送信 (出力) |

| 51 | GP111 | SPI_2_FS1 | GPIO, SPI2 チップ・セレクト 1 (出力) |

| 53 | GP110 | SPI_2_FS0 | GPIO, SPI2 チップ・セレクト 0 (出力) |

| 55 | GP109 | SPI_2_CLK | GPIO, SPI2 クロック出力 |

| 57 | GP115 | SPI_2_TXD | GPIO, SPI2 データ送信 (出力) |

| 59 | GP114 | SPI_2_RXD | GPIO, SPI2 データ受信 (入力) |

| 46 | GP131 | UART_1_TX | GPIO, UART1 データ送信※8 (出力) |

| 61 | GP130 | UART_1_RX | GPIO, UART1 データ受信 (入力) |

| 63 | GP129 | UART_1_RTS | GPIO, UART1 送信要求 (出力) |

| 65 | GP128 | UART_1_CTS | GPIO, UART1 送信可能 (入力) |

| 44 | GP84 | SD_0_CLK_FB | GPIO, SD クロック・フィードバック |

| 58 | GP78 | SD_0_CLK | GPIO, SD クロック出力 |

| 60 | GP77 | SD_0_CD# | GPIO, SD カード検出入力 (負論理) |

| 62 | GP79 | SD_0_CMD | GPIO, SD コマンド |

| 66 | GP80 | SD_0_DAT0 | GPIO, SD データ 0 |

| 70 | GP81 | SD_0_DAT1 | GPIO, SD データ 1 |

| 64 | GP82 | SD_0_DAT2 | GPIO, SD データ 2 |

| 68 | GP83 | SD_0_DAT3 | GPIO, SD データ 3※9 |

| 67 | OSC_CLK_OUT_0 | 19.2 MHz 高速クロック出力 | |

| 31 | RCVR_MODE | ファームウェア・リカバリー・モード | |

| 69 | FW_RCVR | ファームウェア・リカバリー (起動時に正論理) | |

| 29,38,40,49 | 未使用 | ||

4 外部インターフェース・ピンと電気特性

あらゆるIntel® Edisonの入出力(USBを除く)は1.8 V信号です。

4.1 クロック

Intel® Edisonは2つのクロックを出力します。32 kHzのスリープ・クロックは7ピン、および高周波数19.2 MHzのクロックは67ピンに接続されています。スリープ・クロックは±5mAのドライブ能力があり、SoCがスリープ状態にあるときに出力を供給するように設定することができます。表28で示される、GPIOバッファー(1.8 V)DC仕様を参照してください。

外部のトレースの長さによっては、クロックをバッファする必要があります。

4.1.1 19.2 MHz OSC クロック出力仕様

表6にOSC_CLK[4:0]とラベルされたクロックの仕様を示します。

表6 19.2 MHz OSC_Clock 出力

| シンボル | パラメーター | 最小 | 典型 | 最大 | 単位 | 図 | 注記 |

|---|---|---|---|---|---|---|---|

| 周波数 | 19.2 | – | MHz | 2, 4 | |||

| TRISE/TFALL | 立ち上がりと立ち下り時間 | 1 | – | 5 | ns | 1, 3 | |

| Duty cycle | デューティー・サイクル | 45 | – | 55 | % | 2 | |

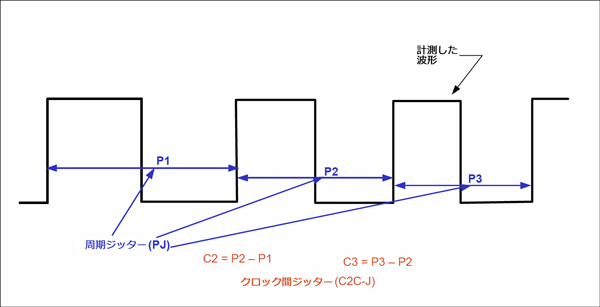

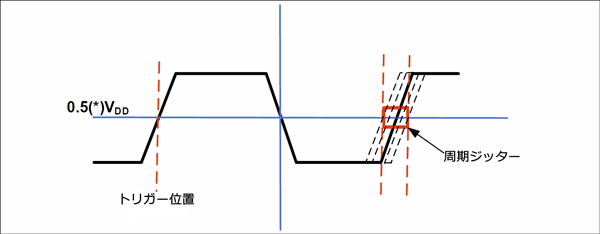

| C2C-J | サイクル間ジッター (ピーク) | – | – | 300 | ps | 図4 | 2, 5 |

| PJ | 周期ジッター (ピークからピーク) | – | – | 350 | ps | 図4, 図5 | 2, 6 |

| 長期精度 | –100 | 0 | +100 | ppm | 7 |

注記:

- エッジ・レートは20%~80%を1.8 V供給で測定しています。

- 周波数とデューティー・サイクルに関しては50%を1.8 V供給で測定しています。デューティー・サイクルは3つ以上の測定値で10 Kサイクルについて測定します。

- 出力は25~200 mmの長さのトレース、2~5 pFの遠端負荷、10 pFのESD、および30~75 Ωのボード・インピーダンスに基づきます。

- 1/2への分周(9.6 MHzの周波数を得られる)および1/4への分周(4.8 MHzの周波数を得られる)のオプションが選択可能です。その他詳細については、Merrifield Platform Firmware Architecture Specification (FAS) for Selected Targeted Accountsの記載を参照してください。

- サイクル間ジッターは、隣接している2つのサイクルの間にどの程度クロック周期が変化するかを示します。周期ジッターに一次階差操作を行うことによって、図4のC2とC3によって示されるように発見することができます。ピークのサイクル間ジッターは最大で10以上の1000サイクルの絶対値の測定値で、JEDEC Specification(JESD65B)のSkew Specifications for Standard Logic Devices(標準ロジック・デバイスのためのスキュー仕様)によって定義されています。

- 周期ジッターの値は、無限残光にセットしたディスプレイで完全な1クロック周期を表示するようにオシロスコープを調整することで測定できます。スコープのトリガーを最初のエッジにセットします。これによって周期ジッターは2番目のエッジの拡散/ピークからピークの値を測定することによって得ることができます。周期ジッターは最大で3以上の10,000サイクルの測定値で、JEDEC Specification(JESD65B)のSkew Specifications for Standard Logic Devices(標準ロジック・デバイスのためのスキュー仕様)によって定義されています。

- 長期精度は水晶とプラットフォームの設計によります。±50 ppmに合致する短期精度は長期精度仕様を満たします。

図4 クロック・ジッターの定義

図5 周期ジッターの測定方法

4.1.2 RTCクロック仕様

表7にPMICによって駆動されるSoC用の32.768 kHzのクロック仕様を示します。

表7 RTCクロック入力仕様

| シンボル | パラメーター | 最小 | 典型 | 最大 | 単位 | 注記 |

|---|---|---|---|---|---|---|

| 周波数 | – | 32.768 | kHz | |||

| 長期精度 | –100 | 0 | +100 | ppm |

4.2 I2C インターフェース

Intel® Edisonは、I2C1とI2C6という2つのI2C インターフェースを備えています。41ピンと43ピンによるI2C1は、IAコアに直接接続した汎用I2Cインターフェースです。45ピンと47ピンによるI2C6は、IAコアと接続するI2C6またはシステム・コントローラー・ファブリックと接続するI2C8(MCUによってコントロールされる)として構成できます。初期リリースのIntel® Edisonは、I2C1とI2C6だけが使用可能です。これら両方のインターフェースは、I2Cとして構成されている際にはオープン・コレクターです。GPIOとして構成されている際には、標準プル・アップ出力にすることができます。

I2Cモジュールは以下のモードで動作することができます:

- スタンダード・モード(最大100 kbpsまでのデータ・レート)

- ファスト・モード(最大400 kbpsまでのデータ・レート)

- ハイスピード・モード(最大3.4 Mbpsまでのデータ・レート)

- SoCは常にI2Cマスターで、マルチマスター・モードには対応していません。

- SoCはスレーブ・デバイスによるクロック・ストレッチ要求に対応しています。

- 7ビットおよび10ビットのアドレス・モードの両方をサポートしています。

I2C6がI2C8として構成されているときには、スタンダードまたはファスト・モードでのみ動作します。

4.2.1 標準仕様準拠

- I2C–Bus Specification and User Manual Revision 03 dated June 2007.

(I2Cバス仕様書およびユーザー・マニュアル リビジョン03 2007年6月付け)

4.2.2 I2C スタンダード/ファスト・モード電気特性

4.2.2.1 I2C スタンダード/ファスト・モードAC仕様

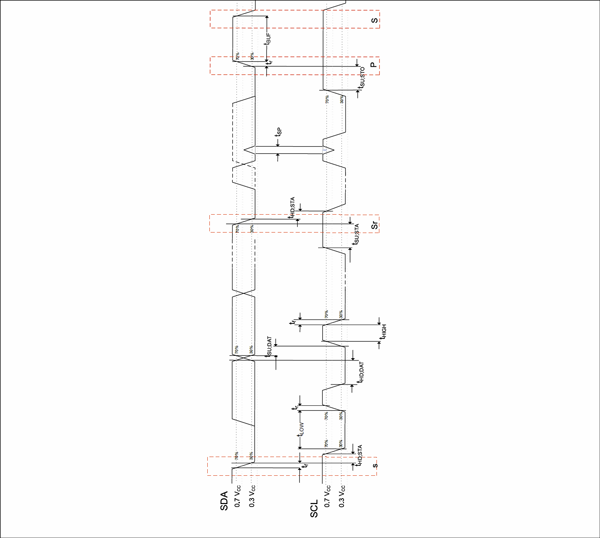

表8 スタンダード/ファスト・モードI2Cバス用デバイスのためのAC仕様

| シンボル | パラメーター | スタンダード | ファスト | 単位 | 注記 | ||

|---|---|---|---|---|---|---|---|

| 最小 | 最大 | 最小 | 最大 | ||||

| fSCL | SCLクロック周波数 | 0 | 100 | 0 | 400 | KHz | |

| tHD: STA | ホールド時間(繰り返し)START状態。この周期の後に最初のクロック・パルスが生成されます。 | 4.0 | – | 0.6 | – | μs | |

| tLOW | SCLクロックのLOW周期 | 4.7 | – | 1.3 | – | μs | |

| tHIGH | SCLクロックのHIGH周期 | 4.0 | – | 0.6 | – | μs | |

| tSU: STA | 繰り返されたSTART状態のためのセットアップ時間 | 4.7 | – | 0.6 | – | μs | |

| tHD: DAT | データのホールド時間: I2Cバス・デバイス | 0 | – | 0 | – | ns | 3 |

| tSU: DAT | データのセットアップ時間 | 250 | – | 100 | – | ns | 1 |

| tr | SDAおよびSCLの両信号の立ち上がり時間 | – | 1000 | 20 + 0.1Cb | 300 | ns | 2, 表9 |

| tf | SDAおよびSCLの両信号の立ち下がり時間 | 10 | 300 | 1 | 300 | ns | 4, 表9 |

| tSU: STO | STOP状態のためのセットアップ時間 | 4.0 | – | 0.6 | – | μs | |

| tBUF | STOPとSTART状態の間のバス・フリー時間 | 4.7 | – | 1.3 | – | μs | |

| Cb | 各バス・ラインのための容量負荷 (=トレース容量 + デバイス負荷) | – | 400 | – | 400 | pF | I |

| VnL | それぞれの接続デバイスのためのLOWレベルにおけるノイズ・マージン (ヒステリシスを含む) | 0.1 VDD | – | 0.1 VDD | – | V | |

| VnH | それぞれの接続デバイスのためのHIGHレベルにおけるノイズ・マージン (ヒステリシスを含む) | 0.2 VDD | – | 0.2 VDD | – | V | |

注記:

- スタンダード・モードのI2Cバス・システムでは、ファスト・モードのI2Cバス・デバイスを使用することができますが、tSU; DAT ≥ 250 nsを満たす必要があります。これはデバイスがSCL信号に対するLOW周期を延長しないのであれば、自動的に満たすことになります。デバイスがSCL信号に対するLOW周期を延長するなら、SCLラインが解放される(スタンダードモードのI2Cバス仕様の通りに)tr max + tSU;DAT = 1000 + 250 = 1250 ns以内にSDAラインに次のデータ・ビットを出力しなければなりません。

- Cb = 1つのバス・ラインの全キャパシタンスのピコファラッドです。

- tHD;DATの最大値はスタンダードモードとファストモードのために、3.4μsから0.9μsになることがありますが、tVD;DATあるいはtVD;ACKの遷移時間の最大値よりは少なくなければなりません。デバイスがSCL信号に対するLOW周期(tLOW)を延長しないのであれば、この最大値を満たすだけで構いません。もし、SCLのクロックを延長するのであれば、クロックをリリースする前のデータのセットアップ時間は必ず有効です。

- I2C仕様から外れ、20 + 0.1 Cbの最小の立ち下がり時間を必要とします。

表9 I2Cスタンダード/ファスト・モードにおけるSCLとSDAに対するプルアップ強度の設定

| Cb | 内部プルアップ値 | 電流アシスト設定 | 注記 |

|---|---|---|---|

| Cb ≤ 14 pF | 20,000 | NA | 1 |

| 14 pF ≤ Cb ≤ 144 pF | 2000 | NA | 1 |

| 40 pF ≤ Cb ≤ 400 pF | 910 | NA | 1, 2 |

注記:

- 内部プルアップ値はCbの値によってファームウェアのMIPヘッダーで設定する必要があります。

- Cbが350 pF以上となる場合にはボード上に外付けのプルアップを必要とすることがあります。さらなる指針についてはIntelの代表者にご連絡ください。

図6 I2Cバス上のスタンダード/ファスト・モードのデバイスのタイミング定義

4.2.2.2 I2C スタンダード/ファスト・モード DC仕様

表10 I2Cスタンダード/ファスト・モードのデバイスのDC仕様

| シンボル | パラメーター | スタンダード (100 kHz) | ファスト (400 kHz) | 単位 | 注記1 | ||||

|---|---|---|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | 最小 | 典型 | 最大 | ||||

| TSP | 入力フィルターによって抑制するスパイクのパルス幅。 | 0 | – | 54 | 0 | – | 54 | ns | 2 |

| VOL | 出力Low電圧。 | – | – | VDD * 0.2 | – | – | VDD * 0.2 | V | ポート 0 ~ 2 および 4 ~ 7 |

| VOL | 出力Low電圧。 | – | – | 90 | – | – | NA | mV | ポート 3 |

| VOH | 出力High電圧。 | VDD * 0.9 | – | – | VDD * 0.9 | – | – | V | |

注記:

- 他のすべてのDC仕様については、表28に示されているGPIOバッファDC仕様を参照してください。

- I2C仕様を逸脱し、ファスト・モードのためのTSPは最大50 nsでなければなりません。

4.2.2.3 I2Cハイ・スピード・モードの電気特性

注記: I2Cハイ・スピード・モードのAC仕様はCb = トレース容量 + デバイス負荷でCb ≤ 100 pFを前提としています。

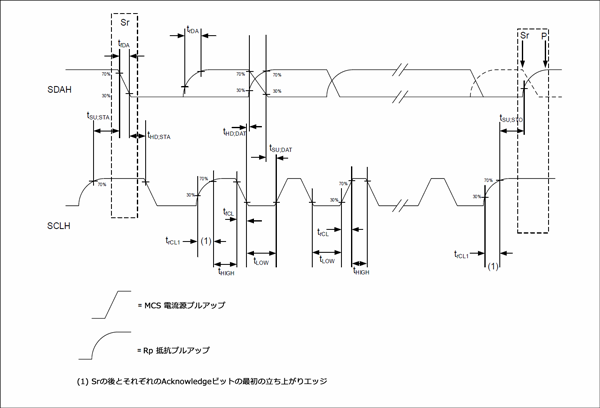

表11 ハイ・スピード・モードI2Cバス用デバイスのためのAC仕様

| シンボル | パラメーター | ハイ・スピード・モード | 単位 | 図表 | 注記 | |

|---|---|---|---|---|---|---|

| 最小 | 最大 | |||||

| fSCL | SCLクロック周波数 | 0 | 2.8 | MHz | ||

| tSU:STA | 繰り返されたSTART状態のためのセットアップ時間 | 160 | – | ns | ||

| tHD:STA | ホールド時間(繰り返し)START状態 | 160 | – | ns | ||

| tLOW | SCLクロックのLOW周期 | 160 | – | ns | ||

| tHIGH | SCLクロックのHIGH周期 | 60 | – | ns | ||

| tHD:DAT | データのホールド時間: I2Cバス・デバイス | 0 | – | ns | ||

| tSU:DAT | データのセットアップ時間 | 10 | – | ns | ||

| tr CL | SCL信号の立ち上がり時間 | 10 | 40 | ns | ||

| tf CL | SCL信号の立ち下がり時間 | 1 | 40 | ns | ||

| trCL1 | 繰り返されたSTART状態の後と応答ビットの後のSCL信号の立ち上がり時間 | 10 | 40 | ns | ||

| tr DA | SDAH信号の立ち上がり時間 | 10 | 80 | ns | 表12 | |

| tf DA | SDAH信号の立ち下がり時間 | 1 | 80 | ns | 表12 | 1 |

| tSU:STO | STOP状態のためのセットアップ時間 | 160 | – | ns | ||

| VnL | それぞれの接続デバイスのためのLOWレベルにおけるノイズ・マージン (ヒステリシスを含む) | 0.1 VDD | – | V | ||

| VnH | それぞれの接続デバイスのためのHIGHレベルにおけるノイズ・マージン (ヒステリシスを含む) | 0.2 VDD | – | V | ||

注記:

- I2C仕様から外れ、20 + 0.1 Cbの最小の立ち下がり時間を必要とします。

表12 I2Cハイ・スピード・モードにおけるSDAに対するプルアップ強度の設定

| Cb | 内部プルアップ値 | 電流アシスト設定 |

|---|---|---|

| Cb < 40 pF | 2 kΩ | NA |

| 40 pF ≤ Cb ≤ 100 pF | 910 Ω | NA |

注記:

- SDA信号のためのCbによって、ファームウェアのMIPヘッダーで内部プルアップ値を設定する必要があります。

表13 I2Cハイ・スピード・モードにおけるSCLに対するプルアップ強度の設定

| Cb | 内部プルアップ値 | 電流アシスト設定1 | 注記 |

|---|---|---|---|

| Cb < 30pF | 2 kΩ | 0x1 | |

| 30 pF ≤ Cb ≤ 40 pF | 2 kΩ | 0x4 | 2 |

| 40 pF ≤ Cb ≤ 70 pF | 2 kΩ | 0x5 | |

| 70 pF ≤ Cb ≤ 90 pF | 2 kΩ | 0xD | |

| 90 pF ≤ Cb ≤ 100 pF | 2 kΩ | 0xE |

注記:

- 内部プルアップ値と電流アシスト設定はCbの値によってファームウェアのMIPヘッダーで設定する必要があります。

- この設定はPMICと通信する際に使用するI2C Port 0に適用されます。

図7 I2Cバスでハイ・スピードモード用デバイスのタイミングの定義

4.2.2.4 I2C ハイ・スピード・モードDC仕様

表14 ハイスピード・モードのI2Cバス・デバイス用DC仕様

| シンボル | パラメーター | ハイ・スピード 2.8 MHz | 単位 | 注記1 | ||

|---|---|---|---|---|---|---|

| 最小 | 典型 | 最大 | ||||

| TSP | 入力フィルターによって抑制するスパイクのパルス幅。 | – | – | 12 | ns | 2 |

| VOL | 出力Low電圧。 | – | – | VDD * 0.2 | V | |

| VOH | 出力High電圧。 | VDD * 0.9 | – | – | V | |

注記:

- 他のすべてのDC仕様については、表28に示されているGPIOバッファDC仕様を参照してください。

- I2C仕様を逸脱し、TSPは最大10 nsでなければなりません。

4.3 SDカード・インターフェース

SD 3.0準拠のインターフェースが44ピン、58ピン、60ピン、62ピン、64ピン、66ピンおよび70ピンにより使用可能です。SDメモリーの主な特徴:

- 最大50MHzのホスト・クロック

- 専用カード検出信号のみでカードの検出(挿抜)をサポート。

- SD Host Controller Standard Specification version 3.0(SDホスト・コントローラー標準仕様 バージョン 3.0)を満たします。

- SDメモリーのみをサポート。

- 2.85 Vデバイスをサポートするために、外部にレベル変換を必要とします。

4.3.1 標準仕様準拠

- SD Specifications Physical Layer Specification—v3.01

(SD仕様 物理レイヤー仕様-v3.01)

4.3.2 SD/SDIO AC仕様

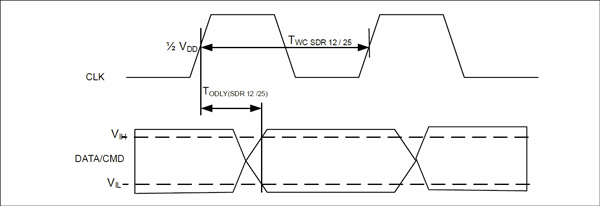

表15 SD AC仕様

| シンボル | パラメーター | Port 0 (SD) | Port 1 (SDIO) | 単位 | 図表 | 注記 | ||

|---|---|---|---|---|---|---|---|---|

| 最小 | 最大 | 最小 | 最大 | |||||

| Twc(DDR50) | DDR50モードのためのCLKサイクル・タイム | 20 | – | 20 | – | ns | 図8 | |

| Twc(SDR25) | SDR25モードのためのCLKサイクル・タイム | 20 | – | 20 | – | ns | 図9 | |

| Twc(SDR12) | SDR12モードのためのCLKサイクル・タイム | 40 | – | 40 | – | ns | ||

| TDC | クロック・デューティー・サイクル | 45 | 55 | 45 | 55 | % | ||

| TODLY(DDR50) | SDIO_DへのSD_CLK遷移エッジ | 1.9 | 4.6 | 2.0 | 4.5 | ns | 図8 | 4 |

| TODLY(SDR25) | SDIO_DへのSD_CLK立ち上がりエッジ | 1.9 | 11.6 | 3.2 | 11.5 | ns | 図9 | 4 |

| TODLY(SDR12) | SDIO_DへのSD_CLK立ち上がりエッジ | 1.9 | 11.6 | 3.2 | 11.5 | ns | 4 | |

| TSU_SOC | SoCセットアップ時間(クロックの前に妥当なデータが送出された場合) | 2.4 | – | 1.3 | – | ns | SDR12/25: 図10 DDR50: 図8 | 4 |

THD_SOC

| SoCホールド時間(クロックの後に妥当なデータが送出された場合) |

1.7 |

– |

2.2 |

– |

ns |

SDR12/25: 図10 DDR50: 図8 |

4 |

|

| TRISE CLK/TFALL CLK | クロックの立ち上がりおよび立ち下がり時間 | 0.5 | 4 | 0.5 | 4 | ns | 1, 2, 3, 5 | |

注記:

- 0.25~4.0 inchのトレース長に基づく、Port 0のための2~5 pFの遠端負荷、およびPort 1のための2~10 pFの遠端負荷、およびボードのインピーダンスによる25~75Ω。これはPort 1上の40 pFとPort 0上の35 pFの集合負荷に相当します。

- 最短時間はSDIO Specification 3.0(SDIO仕様3.0)から逸脱しますが、仕様には定義されていません。

- 0.58 ~ 1.27 Vで測定しました。

- SoCで測定しました。

- Port 0のためのレベル変換およびPort 1のための終端デバイスを計測しました。

図8 SD/SDIO タイミング・ダイアグラム (DDR50)

図9 SD/SDIO 出力タイミング・ダイアグラム (SDR 12/25)

図10 SD/SDIO 入力タイミング・ダイアグラム (SDR12/25)

4.3.3 SD/SDIO DC仕様

表16にSD/SDIO DC仕様を示します。ここにリストアップされていない、他のすべてのDC仕様については表28を参照してください。

表16 SD/SDIO DC仕様

| シンボル | パラメーター | 最小 | 典型 | 最大 | 単位 | 注記 |

|---|---|---|---|---|---|---|

| VOL | 出力Low電圧 | – | – | 0.125*VDD1 | V | 1, 2. Port 0. |

| VOH | 出力High電圧 | 0.75*VDD1 | – | – | V | 1, 2. Port 0. |

| VOL | 出力Low電圧 | – | – | 0.45 | V | 1, 2. Port 1. |

| VOH | 出力High電圧 | 1.4 | – | – | V | 1, 2. Port 1. |

注記:

- IOH/IOLは2mAと仮定します。

- Port 0のためのレベル変換およびPort 1のための終端デバイスを計測しました。

4.4 UARTインターフェース

2つのUARTが使用可能です: UART1はフロー・コントロールを備え、UART2はフロー・コントロールを省いています。UART1インターフェースは46ピン、63ピン、61ピンおよび54ピンで使用できます。UART2は22ピン、27ピンおよび27ピンで使用できます。UARTは以下の通りです:

- 16550準拠

- 64バイトのバッファー

- ボー・レートは300 bpsから3.686 Mbps

UART2のもう1つの機能はLinuxデバッグ・シリアル・ポートです。

SoCは16550準拠のUARTコントローラーを3インスタンス、サポートしています(このIPのバッファーは64バイトを確保しており、それは16750に準拠しています。レジスター・セットは16550と互換性が確保されています)。

それぞれのUARTインターフェースは以下のボー・レート(TBAUD)をサポートします: 3.6864 M, 921.6 k, 460.8 K, 307.2 K, 230.4 K, 184.32 K, 153.6 K, 115.2 K, 57.6 K, 38.4 K, 19.2 K, 9.6 K, 7.2 K, 4.8 K, 3.6 K, 2.4 K, 1.8 K, 1.2 K, 600, および 300。

4.4.1 UART AC仕様

表17 UART AC仕様

| シンボル | パラメーター | 最小 | 最大 | 単位 | 注記 |

|---|---|---|---|---|---|

| TRISE | 最大立ち上がり時間 | 5 | 25 | ns | 1, 2 |

| TFALL | 最大立ち下がり時間 | 5 | 25 | ns | 1, 2 |

| TUARTFIL | UARTサンプリング・フィルター周期 | 26 | – | ns | 3 |

注記:

- 負荷キャパシタンスが5~65 pF(トレース長は最大100 mm)およびボード・インピーダンスが25~75 Ωに基づきます。

- 10~90%で測定しました。

- スタートおよびストップ・ビットを含む各ビットを、プリスケーラー値の1/4で抽出します。それぞれのプリスケーラー・サイクルには、TUARTFILによる周期が適用されます。

図11 UARTタイミング・ダイアグラム

4.4.2 UART DC仕様

表28で示される、GPIOバッファー(1.8 V)DC仕様を参照してください。

4.5 I2Sインターフェース

I2Sインターフェースは、50ピン、52ピン、54ピンおよび56ピンで使用可能です。以下のI2Sモードのすべてが未検証で変更が発生する可能性があります。表18にI2Sポートで使用可能なフォーマット一覧を示します。

表18 Intel® Edison I2S 使用可能なフォーマット

| モード | 優先度 | フレーム・レート | ビット数/サンプル | スロット数 | フレームからのデータ・オフセット | フレーム極性 | フレーム幅 | フレーム・レート誤差 | 注記 | |

|---|---|---|---|---|---|---|---|---|---|---|

| I2Sマスター | 1 | 192K, 96K, 48K, 16K, 8K | 16, 24 | 2 | 1 | 0-左, 1-右 | 50/50 | 0% | スタンダード I2S プロトコル。フレームは50%のデューティー・サイクル | |

| PCM スレーブ – SFS | 1 | 192K, 96K, 48K, 44.1K, 16K, 8K | 16, 24 | 192 kHz: 2 96 kHz: 4 それ以外のすべて: 1 ~ 6 | 0 | 高 | ||||

| PCM スレーブ – LFS | 1 | 192K, 96K, 48K, 44.1K, 16K, 8K | 16, 24 | 192 kHz: 2 96 kHz: 4 それ以外のすべて: 1 ~ 6 | 0 | 高 | ||||

| PCM マスター – SFS | 1 | 192K, 96K, 48K, 16K, 8K | 16, 24 | 192 kHz: 2 それ以外のすべて: 1 ~ 4 | 0 | 高 | 1ビットのクロック幅 | 0% | 立ち上がりエッジ・フレームにセンシティブ。さらにフレームからのデータ・オフセットのオプションをサポートする設計。 | |

| PCM マスター – LFS | 1 | 192K, 96K, 48K, 16K, 8K | 16, 24 | 192 kHz: 2 それ以外のすべて: 1 ~ 4 | 0 | 高 | nビットのクロックのための1ビット | 0% | nは1つのスロットの幅。1スロット以上の幅をサポートする設計となっている。 | |

| 左詰めマスター | 2 | 192K, 96K, 48K | 16, 24 | 2 | 0 | 0-左, 1-右 | 50/50 | 0% | フレーム信号上の極性をフリップすることをサポートする設計。 | |

| I2S スレーブ | 3 | 192K, 96K, 48K, 44.1K | 16, 24 | 2 | 0 | 0-左, 1-右 | 50/50 | 0% | ||

| 左詰めスレーブ | 3 | 192K, 96K, 48K | 16, 24 | 2 | 0 | 0-左, 1-右 | 50/50 | 0% | ||

| 右詰め | 非サポート | |||||||||

SoCには3つのI2Sポート(I2S 0, 1, 2と名付けられている)があります。

表19 I2Sポート概要(リファレンス・デザインによる実装)

| ポート番号 | サポートするモード | 公称電圧 | 最大動作周波数 | 注記 |

|---|---|---|---|---|

| 0 | マスターおよびスレーブ | 1.8 V | 9.6 MHz | リファレンス・デザインのモデムでインターフェースをスレーブ・モードで使用する。モデムはPCMショート・フレーム・モードを使用する。 |

| 1 | マスターおよびスレーブ | 1.8 V | 9.6 MHz | リファレンス・デザインのBluetooth*/FMモジュールでインターフェースをスレーブ・モードで使用する。 |

| 2 | マスターおよびスレーブ | 1.8 V | 9.6 MHz | リファレンス・デザインのオーディオ・コーデックでインターフェースをスレーブ・モードで使用する。 |

4.5.1 I2S AC仕様

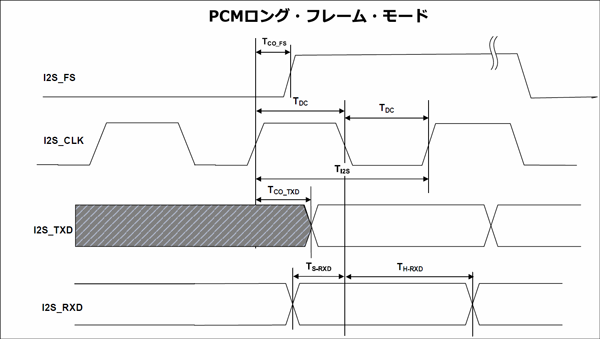

4.5.1.1 I2Sマスター・モードにおけるAC仕様

表20 I2SマスターACタイミング

| シンボル | パラメーター | 最小 | 最大 | 単位 | 図表 | 注記 |

|---|---|---|---|---|---|---|

| TDC | クロック・デューティー・サイクル | 45 | 55 | % | I, I, I | |

| TI2S | クロック周波数 | – | 9.6 | MHz | I, I, I | |

| TS-RXD | I2S CLKアクティブ・エッジを考慮したRXDのセットアップ時間。 | 10 | – | ns | I, I, I | 1, 2, 3, 4 |

| TH_RXD | I2S CLKアクティブ・エッジを考慮したRXDホールド時間。 | 10 | – | ns | I, I, I | 1, 2, 3, 4 |

| TCO_TXD | SoCのI2S CLKアクティブ・エッジを考慮したTXDのTco時間。 | – | 10 | ns | I, I, I | 1, 2, 3, 4 |

| TCO-FS | SoCのCLKを考慮したFSのTco時間。 | – | 10 | ns | I, I, I | 1, 2, 3, 4 |

注記:

- 選択されたモードをアクティブ・エッジは参照します。

- I2Sモードの時:

- I2S_TXD – SoCはクロック・エッジの立ち下がりの後にデータの送出を開始します。

- I2S_RXD – SoCはクロック・エッジの立ち上がりの時にデータをラッチします。

- SoCがPCMモードの時:

- I2S_TXD – SoCはクロック・エッジの立ち上がりの後にデータの送出を開始します。

- I2S_RXD – SoCはクロック・エッジの立ち下がりの時にデータをラッチします。

- PCMモードの2つの異なるモード、ショート・フレーム・モードおよびロング・フレーム・モード:

- ショート・フレーム・モード – マスターはI2S-FSの1クロック後にデータをドライブすると仮定します。

- ロング・フレーム・モード – マスターはI2S_FSとデータは同じクロックであると仮定します。

図12 I2SモードにおけるI2Sマスター・ポートのタイミング

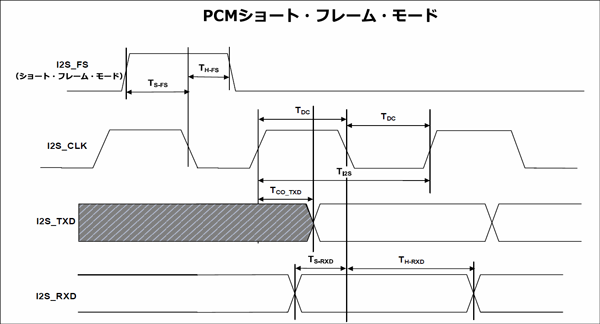

図13 PCMショート・フレーム・モードにおけるI2Sマスター・ポートのタイミング

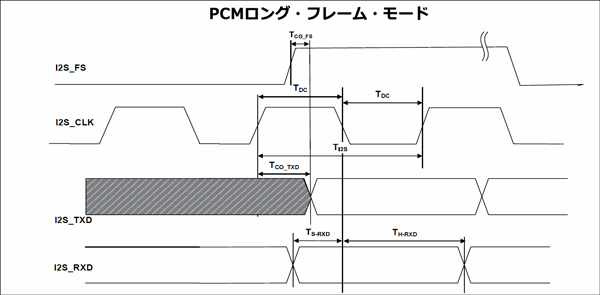

図14 PCMロング・フレーム・モードにおけるI2Sマスター・ポートのタイミング

4.5.1.2 I2Sスレーブ・モードAC仕様

表21 I2Sスレーブ・モードACタイミング・パラメーター

| シンボル | パラメーター | 最小 | 最大 | 単位 | 図表 | 注記 |

|---|---|---|---|---|---|---|

| TDC | クロック・デューティー・サイクル | 40 | 60 | % | 図15, 図16, 図17 | |

| TI2S | クロック周波数 | – | 9.6 | MHz | 図15, 図16, 図17 | |

| TS-RXD | I2S CLKアクティブ・エッジを考慮したRXDのセットアップ時間。 | 18 | – | ns | 図15, 図16, 図17 | 1, 2, 3, 4 |

| TH_RXD | I2S CLKアクティブ・エッジを考慮したRXDホールド時間。 | 0 | – | ns | 図15, 図16, 図17 | 1, 2, 3, 4 |

| TS-FS | I2S CLKアクティブ・エッジを考慮したFSのセットアップ時間。 | 5.1 | – | ns | 図15, 図16, 図17 | 1, 2, 3, 4 |

| TH_FS | I2S CLKアクティブ・エッジを考慮したFSホールド時間。 | 5.1 | – | ns | 図15, 図16, 図17 | 1, 2, 3, 4 |

| TCO_TXD | ホストのI2S CLKアクティブ・エッジを考慮したTXDのTco時間。 | 3.3 | 29.2 | ns | 図15, 図16, 図17 | 1, 2,3, 4 |

| TCO-FS | ホストのFSを考慮したTXDのTco時間。 | 3.3 | 29.2 | ns | 図15, 図17 | 1, 2, 3, 4, 5 |

注記:

- 構成されたモードをアクティブ・エッジは参照します。

- I2Sモードの時:

- I2S_TXD – SoCはクロック・エッジの立ち下がりの後にデータの送出を開始します。

- I2S_RXD – SoCはクロック・エッジの立ち上がりの時にデータをラッチします。

- SoCがPCMモードの時:

- I2S_TXD – SoCはクロック・エッジの立ち上がりの後にデータの送出を開始します。

- I2S_RXD – SoCはクロック・エッジの立ち下がりの時にデータをラッチします。

- PCMモードの2つの異なるモード、ショート・フレーム・モードおよびロング・フレーム・モード:

- ショート・フレーム・モード – マスターはI2S-FSの1クロック後にデータをドライブすると仮定します。

- ロング・フレーム・モード – マスターはI2S_FSとデータは同じクロックであると仮定します。

- TCO-FSは、I2SモードとPCMショート・フレーム・モードにはあてはまりません。

図15 I2SモードにおけるI2Sスレーブ・ポート・タイミング・パラメーター

図16 PCMショート・フレーム・モードにおけるI2Sスレーブ・ポート・タイミング・パラメーター

図17 PCMロング・フレーム・モードにおけるI2Sスレーブ・ポート・タイミング・パラメーター

4.5.2 I2S DC仕様

表22に記載のないI2S DC仕様については、表28に掲載されたGPIOバッファーDC仕様を参照してください。

表22 I2SバッファーDC仕様

| シンボル | パラメーター | 最小 | 典型 | 最大 | 単位 | 注記 |

|---|---|---|---|---|---|---|

| VOH | High電圧出力 | 0.8 * VDD | – | – | V | IOHの最大を計測。 |

| VOL | Low電圧出力 | – | – | 0.2 * VDD | V | IOLの最大を計測。 |

4.6 SPIインターフェース

SPIインターフェースは、51ピン、53ピン、55ピン、57ピンおよび59ピンで使用可能です。このインターフェースは2つのチップの選択が可能です。

- シングル・フレーム転送では、SoCは連続したクロック・フェーズと極性のための、4つの可能な組み合わせをすべてサポートします。

- マルチプル・フレーム転送では、SoCはSPH=1およびSPO=0または1をサポートします。

- SoCはSPH=0のためのそれぞれのデータ・フレームにおけるスレーブ・セレクト信号を切り替えることができます。

- マスター・モードは25 MHz、スレーブ・モードは16.67MHz。

SoCには4つのSPIポートがあります: SPI 0, 1, 2, および 3。

表23 SPIポートの概要

| ポート番号 | モード | 公称電圧 | 最大周波数 |

|---|---|---|---|

| 0 ~ 3 | マスターおよびスレーブ | 1.8 V | 25 MHz (マスター・モード) 16.67 MHz (スレーブ・モード) |

表24 SPIモード

| ポート番号 | SPO | SPH |

|---|---|---|

| 0 | 0 | 0 |

| 1 | 0 | 1 |

| 2 | 1 | 0 |

| 3 | 1 | 1 |

注記: SPOとSPHはSSP Control Register CTRL1 (SCCR1)で構成することができます。

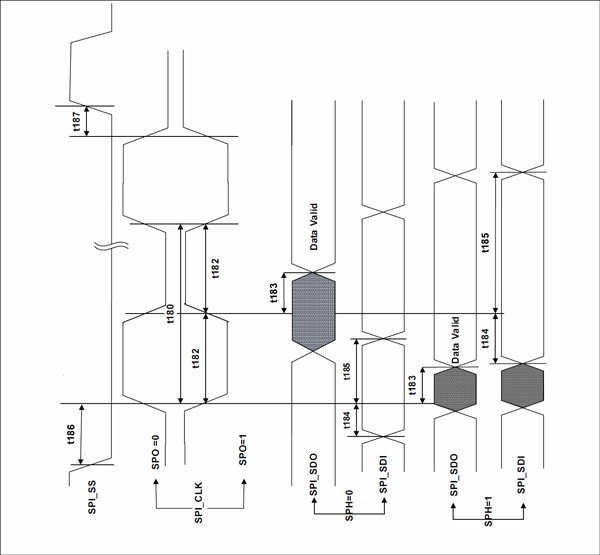

4.6.1 SPIマスターAC仕様

表25 SPIマスターACタイミング

| シンボル | パラメーター | 最小 | 最大 | 単位 | 図表 | 注記 |

|---|---|---|---|---|---|---|

| t180 | シリアル・クロック周波数 | 25 | MHz | 図18 | ||

| t182 | ホストのSPIクロック・デューティー・サイクル | 45 | 55 | % | 図18 | |

| t183 | ホストのシリアル・クロック・エッジを考慮したSPI_SDO (SPI_MOSI)のTco時間 | 0 | 5.4 | ns | 図18 | 3 |

| t184 | ホストのシリアル・クロック・エッジを考慮したSPI_SDO (SPI_MOSI)のセットアップ時間 | 5.2 | – | ns | 図18 | 3 |

| t185 | ホストのシリアル・クロック・エッジを考慮したSPI_SDO (SPI_MOSI)のホールド時間 | 14.3 | – | ns | 図18 | 3 |

| t186 | ホストのシリアル・クロック・エッジを考慮したSPI_SSアサーションのセットアップ時間 | 5.2 | – | ns | 図18 | 3 |

| t187 | ホストのシリアル・クロック・エッジを考慮したSPI_SSデアサーションのホールド時間 | 14.3 | – | ns | 図18 | 3 |

| TRISE/TFALL | 最大立ち上がり/立ち下がり時間 | 0.85 | 10 | ns | 1 | |

| TRISE/TFALL | 最大立ち上がり/立ち下がり時間 | 0.6 | 3 | ns | 2 |

注記:

- 基準点:

- トレース長は最大6 inch

- ボード・インピーダンスは25~75 Ω。

- 合計最大遠端キャパシタンスは40 pF (各負荷 10 pF の 4 負荷)

- 35~65%から計測

- 基準点:

- トレース長は最大4 inch

- ボード・インピーダンスは27~75 Ω

- 合計最大遠端キャパシタンスは10 pF

- 35~65%から計測

- クロック・エッジはSPIポートで使用するモードに依存します。

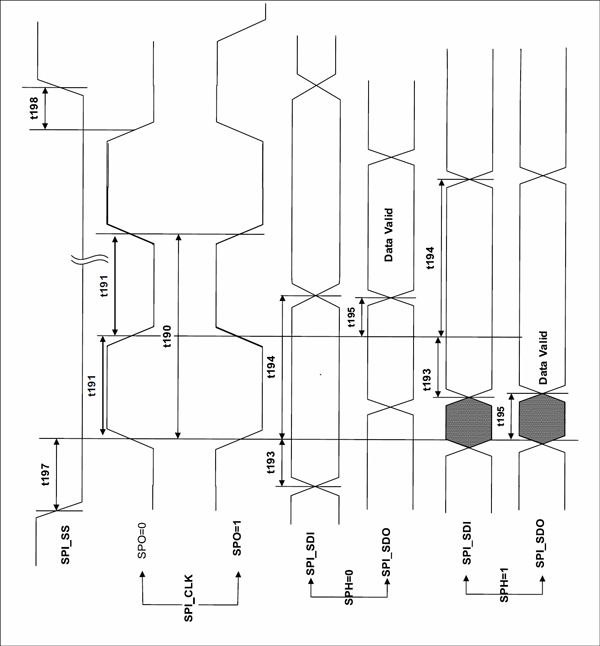

図18 SPIマスター・タイミング

4.6.2 SPIスレーブAC仕様

表26 SPIスレーブACタイミング

| シンボル | パラメーター | 最小 | 典型 | 最大 | 単位 | 図表 | 注記 |

|---|---|---|---|---|---|---|---|

| t190 | シリアル・クロック周波数 | – | – | 16.67 | MHz | 図19 | |

| t191 | クロック・デューティー・サイクル | 45 | – | 55 | % | 図19 | |

| t193 | シリアル・クロック・エッジを考慮したSPI_SDI (MOSI)のセットアップ時間 | 5 | – | – | ns | 図19 | 1 |

| t194 | シリアル・クロック・エッジを考慮したSPI_SDI (MOSI)のホールド時間 | 5 | – | – | ns | 図19 | 1 |

| t195 | シリアル・クロック・エッジを考慮したSPI_SDI (MOSI)のTCO時間 | 5 | – | 21 | ns | 図19 | 1 |

| t197 | シリアル・クロック・エッジを考慮したSPI_SSアサーションのセットアップ時間 | 5 | – | – | ns | 図19 | 1 |

| t198 | シリアル・クロック・エッジを考慮したSPI_SSデアサーションのホールド時間 | 5 | – | – | ns | 図19 | 1 |

注記:

- クロック・エッジは使用するモードに依存します。

図19 SPIスレーブ・タイミング

4.6.3 SPI DC仕様

SPIマスターとスレーブのDC仕様については表28を参照してください。

4.7 GPIO(汎用入出力)

多くの汎用入出力を外部インターフェースで使用することができます。これらは以下のピンに割り当てられます:24、25、26、28、30、32、34、42、および48。これらのいくつかは、外付けのセンサーをサポートするための割り込みの代替機能に使用することができます。セクション4(I2C、I2S、UARTなど)で取り上げたすべてのインターフェースを使用しないのであれば、これらに替えて汎用I/Oを使用することができます。

ピン・モードがGPIOを選択しているとき、出力または入力としてモードを設定することができます。入力として設定すると、GPIOは割り込みまたはウェイク・ソース(スリープ解除ソース)として機能します。入力は、プルアップまたはプルダウンを選択することができます。プルアップは、2、20、あるいは50kΩを選択できます。また、I2Cピンには910Ωの追加抵抗があります。汎用モードの場合、入力するGPIO信号はデフォルトでグリッジ・フィルターを通しますが、その前にエッジ検出レジスターに到達します。

パルスをエッジ検出レジスターが検出することを保証するために、パルスは5クロック・サイクル以上の長さがあるべきです。

- SoCがS0ステートの場合、50 MHzクロックのため、100 nsが必要です。

- SoCがS0i2ステートの場合、19.2 MHzクロックのため、260 nsが必要です。

- SoCがS0i3ステートの場合、32 kHzクロックのため、155.5 μsが必要です。

ほとんどのGPIOが可能なピンのすべてが、リセットがアサートされている間、GPIOの入力として構成されています。そして、これは別の構成に変更されるまで保持されます。GPIOは個別にクリアするかまたはセットすることで出力にすることができます。これらは、スタンバイ状態に入るとき、いずれかの状態のためにあらかじめ設定することができます。出力のドライブは±3mAです。

GPIOバッファーはSoCが様々なインターフェースを横断して使用します: 各GPIO、I2C、I2S、MIPI PTI、SPI、SDIO、SVID、UART、PWM、CAMERA SB、JTAGおよびULPI、FAST-INT、OSC_CLK_OUT、OSC_CLK_CLTRL。

4.7.1 GPIO AC仕様

表27にGPIOとして使用する際の信号のAC仕様を示します。※10

表27 GPIOバッファーAC仕様

| シンボル | パラメーター | 最小 | 最大 | 単位 | 注記 |

|---|---|---|---|---|---|

| TRISE | 最大立ち上がり時間 | 5 | 45 | ns | 1, 2 |

| TFALL | 最大立ち下がり時間 | 5 | 45 | ns | 1, 2 |

注記:

- 合計最大キャパシタンスは150 pFを基準としています。

- 10 ~ 90%を計測しています。

4.7.2 GPIO DC仕様

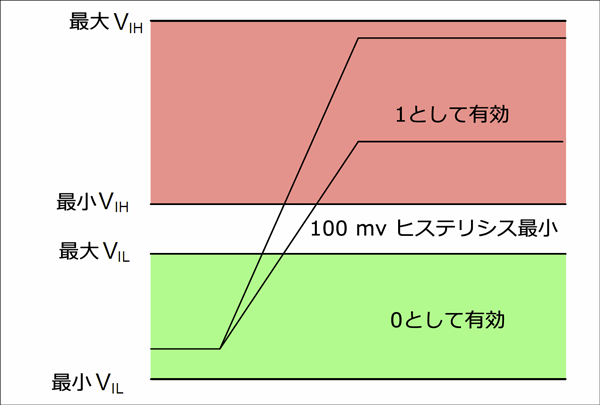

表28 GPIOバッファーDC仕様

| シンボル | パラメーター | 最小 | 典型 | 最大 | 単位 | 注記 |

|---|---|---|---|---|---|---|

| VDD | 供給電圧 | 1.71 | 1.8 | 1.89 | V | |

| VIH | 入力High電圧 | 0.65 * VDD | – | – | V | |

| VIL | 入力Low電圧 | – | – | 0.35 * VDD | V | |

| VOH | 出力High電圧 | VDD – 0.45 | – | – | V | IOHの最大を計測 |

| VOL | 出力Low電圧 | – | – | 0.45 | V | IOLの最大を計測 |

| VHYSTERESIS | 入力ヒステリシス | 100 | – | – | mv | |

| IOH/IOL | VOL/VOHの電流 | -3 | – | 3 | mA | |

| ILI | 入力リーク電流 | -2 | – | 2 | μA | |

| ILO | 出力リーク電流 | -2 | – | 2 | μA | |

| C pin | 入力ピンのキャパシタンス | 2 | – | 5 | pF |

図20 GPIOバッファー入力範囲

4.7.3 GPIOプルアップおよびプルダウン仕様

表29 GPIOプルアップおよびプルダウン仕様

| プルアップおよびプルダウンのオプション | 許容誤差 | 注記 |

|---|---|---|

| 2 kΩ, 20 kΩ, 50 kΩ | ±30% | 各GPIOとして使用できるすべてのピンで使用可能。 |

| 910 Ω | ±30% | I2Cピンに限り使用可能。 |

4.8 PWM(パルス幅変調)

PWM出力として構成できる4つのGPIOを備えます。これらは33ピン、35ピン、37ピンおよび39ピンに割り当てられています。PWMの分解能は8ビットです。

主なPWM変数によって制御されるPWM出力は以下の通りです:

- 以下の方程式でPWM出力周波数とデューティー・サイクルを見積もることができます:

- 対象周波数 ~= 19.2 MHz × Base_unit値 ÷ 256

- 対象PWMデューティー・サイクル ~= PWM_on_time_divisor ÷ 256

表30にPWM設定のいくつかの例を示します。

表30 Intel® Edison PWM設定の例

| 整数部分の PWM_base_unit (bits 29:22) |

分周部分の PWM_base_unit (bits 21:8) |

10進数による値 | 基本単位型 | PWM 周波数 (Hz) | PWM 周期 (μs) | 分解能ビット数 | PWM 刻み |

|---|---|---|---|---|---|---|---|

| 0000_0000b | 00_0100_0000_0000b | 0.0625 | 分周 | 4,688 | 213 | 8 | 0.39% |

| 0000_0000b | 00_0010_0000_0000b | 0.03125 | 分周 | 2,344 | 427 | 8 | 0.39% |

| 0000_0000b | 00_0001_0000_0000b | 0.015625 | 分周 | 1,172 | 853 | 8 | 0.39% |

| 0000_0000b | 00_0000_1000_0000b | 0.0078125 | 分周 | 586 | 1,707 | 8 | 0.39% |

| 0000_0000b | 00_0000_0100_0000b | 0.00390625 | 分周 | 293 | 3,413 | 8 | 0.39% |

| 0000_0000b | 00_0000_0010_0000b | 0.00195325 | 分周 | 146 | 6827 | 8 | 0.39% |

| 0000_0000b | 00_0000_0001_0000b | 0.0009765625 | 分周 | 73.2 | 13,653 | 8 | 0.39% |

| 0000_0000b | 00_0000_0000_1000b | 0.00048828125 | 分周 | 36.6 | 27,307 | 8 | 0.39% |

| 0000_0000b | 00_0000_0000_0100b | 0.000244140625 | 分周 | 18.3 | 54,613 | 8 | 0.39% |

| 0000_0000b | 00_0000_0000_0010b | 0.0001220703125 | 分周 | 9.2 | 109,227 | 8 | 0.39% |

| 0000_0000b | 00_0000_0000_0001b | 0.00006103515625 | 分周 | 4.6 | 218,453 | 8 | 0.39% |

| 0000_0000b | 00_0000_0010_0001b | 0.00201416015625 | 分周 | 151 | 6619 | 8 | 0.39% |

4.8.1 PWM AC仕様

PWM AC仕様については、表27を参照してください。

4.8.2 PWM DC仕様

PWM DC仕様については、表28を参照してください。

4.9 USB(ユニバーサル・シリアル・バス)

Intel® Edison Compute Moduleは1つのUSB 2.0インターフェースがあります。このインターフェースはコードをダウンロードする主な手段です。このインターフェースは以下のピンに割り当てられています:3、16、18、および20。

注記: USB_VBUS信号は20ピンに供給しなければなりません。この信号はIntel® Edisonモジュールにアラートを出すためだけに用いられ、それはホストの(USB)ポートに接続します。

Intel® Edison Compute Moduleはデバイスに電力を供給するために20ピンに供給された電力を使用することはありません。Intel® Edisonは3ピンのID信号を使用して、OTGをサポートするようにデザインされています。OTG電源機能は搭載していません。PSW(21ピン)およびULPIコントローラーからのFAULT(19ピン)の2つの信号は外部の電源スイッチの制御とVBUSの過電流状態を監視するために使用します。図21に外部ハードウェアの構成を示します。

図21 Intel® Edison用の外部USB設計の例

PSW信号は正論理で、外部のVBUS電源スイッチまたはチャージ・ポンプを制御します。

FAULT信号は負論理です。もしUSBホスト・モードを使用しないのであれば、FAULTはGNDと接続すべきです。

SoCはOTGオペレーションで使用するとされたULPIである1つのULPIインターフェースを含みます。

SoCの機能である12-bit UTMI+ Low Pin Interface Specification(ULPI)によるインターフェースにSoCのプラットフォームから独立した外部コンポーネントであるUSB 2.0 OTG v2.0 トランシーバーが接続されてます。

4.9.1 標準仕様準拠

- On-the-Go Supplement to the USB 2.0 Specification, Revision 2.0 (May 2009).

(USB 2.0仕様へのOn-the-Go補足, リビジョン 2.0(2009年5月))

4.10 システム・リセット

Intel® Edisonには2つのシステム・リセット信号PWRBTN#(17ピン)とRESET_OUT#(36ピン)があります。PWRBTN#ピンは、Intel® Edisonモジュールのスリープへ入ったり出たりの状態変化を起こしたり、電源をオフにしたり、ソフトウェアによって構成された状態に遷移したりさせることができる負論理の入力です。RESET_OUT#はオープンドレインで、システム・リセットの後にデフォルトでLowに駆動されます。この信号は、システム・リセットを示すために外部のハードウェアによって用いることができます。Intel® EdisonのI/Oは、RESET_OUT#がHighに遷移するまで不定です。

4.11 ソフトウェア・リカバリー (FWR_RCVRおよびRCVR_MODE)

Intel® Edisonボードには、SoCがファームウェアとOSイメージのダウンロードを強制させるための、ブート中に使用する2つの信号を備えています。これらは工場で使用するためだけのものです。

4.12 電源入力と出力

Intel® Edisonモジュールには5つの電源レールがあります: VSYS、3.3 V、1.8 V、USB_VBUS、およびV_VBAT_BKUP。VSYSはIntel® Edisonモジュール唯一の入力電源レールであり、電圧の範囲は3.15Vから4.5Vまでです。USB_VBUSは、標準のUSB_VBUS入力による4.75Vから5.25Vまでです。このレールはデバイスの電源としては使用しません。Intel® Edisonがデバイスとしてホストのデバイスに接続されていることを確認するためにUSB ULPI PHYによって用いられるのみです。3.3Vと1.8VはIntel® Edisonモジュールをソースとするそれぞれ最大100 mAの電源出力です。

DCINは、Intel® Edisonデバイスがバッテリーまたは外部の電源からのいずれで動作しているかを示す信号です。また、DCINはブートするためにVSYSに必要な電圧レベルを設定します。DCINが未接続またはグラウンドに接続されている場合には、100ミリ秒でVSYSの電圧が2.5Vから3.5Vまで上昇しなければならず、そうでなければブートは中止されます。ブートが中止された時には、電源は2.5V未満に回帰しなければなりません。もし、DCINがVSYSに接続されている時に100ミリ秒にわたってVSYSが2.5 Vを超えているならIntel® Edisonはブートを開始します。

注記: Wi-FiおよびBluetoothの機能性を保証する絶対最小電圧は3.15 Vです。

4.13 V_VBAT_BKUP

PMICには、バックアップ電源のための専用の充電サブシステムがあり、充電式のコイン・セル・バッテリーまたはスーパーキャパシターの使用を許容します。このバックアップ・サブシステムはメイン・システムのバッテリーを交換するような短周期での主電源からの割り込みを許容します。外部のセルは23ピンのV_VBAT_BKUPに接続すべきです。PMICは2.5、3.0、3.15または3.3Vの充電電圧を設定できます。充電電流は、10、50、100または500μAを設定できます。デフォルトの設定は2.5Vと10μAです。

これらの設定を変更するためには、BBCHGRCFGレジスター(表31)を変更する必要があります。ドライバーdrivers/platform/x86/intel_scu_pmic.cによって提供される以下の機能を使用することで、LinuxカーネルからBBCHGRCFGレジスターの8ビット値を読み書きします:

// Read BBCHGRCFG into bbchgrcfg_value

// (BBCHGRCFGを読み出してbbchgrcfg_valueへ格納)

uint8_t bbchgrcfg_value;

int ret;

ret = intel_scu_ipc_ioread8(0x52, &bbchgrcfg_value);

if (ret)

error;

// Set BBCHGRCFG to NEW_BBCHGRCFG_VALUE

// (BBCHGRCFGに新しい値NEW_BBCHGRCFG_VALUEを設定)

int ret;

ret = intel_scu_ipc_iowrite8(0x52, NEW_BBCHGRCFG_VALUE);

if (ret)

error;D5、D6およびD7は0のままにすべきです。

表31 BBCHGRCFG – バッテリー・バックアップ充電器およびメイン・バッテリー充電器IC構成レジスター

| レジスター名 | 読み/書き | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 | 初期値 | アドレス |

|---|---|---|---|---|---|---|---|---|---|---|---|

| BBCHGRCFG | 読み/書き | RSVD | CHGDIS_ACT | BBCHGI[1:0] | BBCHGV[1:0] | BBCHGEN | 0x01 | 0x52 (0x5E) | |||

| ビット | 名称 | 機能 | デフォルト値 |

|---|---|---|---|

| D[7:6] | RSVD | 予約 | 00 |

| D5 | CHGDIS_ACT | 充電用IC無効ピンの動作。メイン・バッテリー充電ICがCHGDISピンがアサートされた際にどのように応じるかを設定します。このビットに設定される値は完全に充電用ICの選択によります。このビットは読み出し専用です。

0 = アサートによってメイン・バッテリー充電用ICを無効にします(電源経路を使用できません)。 |

0 (不揮発) |

| D[4:3] | BBCHGI[1:0] | バックアップ電源の充電電流制限値を設定します。 00 = 10 μA 01 = 50 μA 10 = 100 μA 11 = 500 μA |

00 (不揮発) |

| D[2:1] | BBCHGV[1:0] | バックアップ電源の充電制限値を設定します。 00 = 2.5 V 01 = 3.0 V 10 = 3.15 V 11 = 3.3 V |

00 (不揮発) |

| D0 | BBCHGEN | 0 = バックアップ電源の充電を無効にします。 1 = バックアップ電源の充電を有効にします。 |

1 (不揮発) |

設定例:

- レジスターへの設定: BBCHGRCFG=19

- 電圧: 2.5 V (デフォルト値)

- 電流: 500 μA

- 充電電流: 500 μA

- 放電電流 (消費): 8.0 μA

- 充電電圧: 2.5 V

- 最小RTC保持電圧: 2.05 V

- 電気二重層コンデンサーのキャパシタンス: 0.014F (PAS3225P2R6143/太陽誘電)

- 理論上のバックアップ時間 = 0.014F * (2.5 to 2.05) V / 8 μA = 787.5 秒 = 13 分

- 測定した(実際の)バックアップ時間 = 15 分 20 秒

- 測定した充電完了時間 (0 to 2.5 V) = 2 分 24 秒

4.14 静電気放電 (ESD) 仕様

表32 ESD 性能

| モデル | 通過電圧 | 注記 |

|---|---|---|

| 人体帯電モデル (HBM) | ±1 kV | |

| デバイス帯電モデル (CDM) | ±500 V | 後述で言及される対象を除くすべてのピン |

| デバイス帯電モデル (CDM) | ±250 V | USB3, HDMI, DSI, CSI, および LPDDR3のピン |

注記: 通過電圧は、すべての信号と電源ピンに適用されます。

5 Intel® Edisonへの電力供給

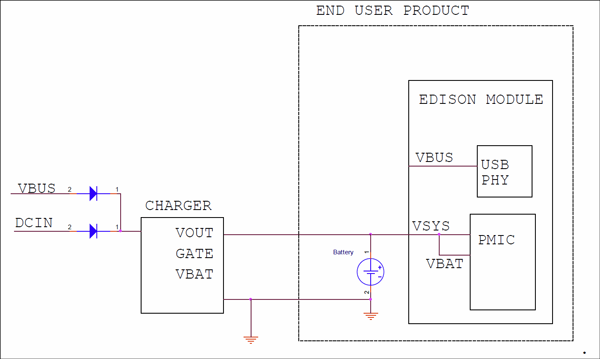

Intel® Edisonはバッテリー電源または壁のAC電源によって動作する多くのデバイスに埋め込まれるでしょう。このためIntel® Edisonは特定の電源供給方法または特定のバッテリー種別および電源容量に依存しないように設計されています。この部分の設計はエンド・ユーザーにゆだねています。インターフェースが使用可能であれば、スマート・バッテリーの残量ゲージとスマート充電器を連携して、I2Cバスに1つのデバイスとして設置することが考えられます。特定のバスに対するソフトウェアの移植はエンド・ユーザーの責任によります。

5.1 主電源(供給) VSYS

Intel® Edisonは唯一の電源入力経路としてVSYS(2ピン、4ピン、および6ピン)を使用します。Intel® Edisonの内部へのこの信号は、VBAT経路に接続されています。VSYSへの電源の供給をバッテリー挿入と解釈して、Intel® Edisonの起動を促します。VSYSへの電圧の範囲は最低3.15Vから最大4.5です(セクション 4.12を参照)。このため、VSYSは標準的なリチウム・イオンバッテリーによって駆動することができます。Intel® Edisonにとって、エンド・ユーザー製品のサイズとコスト感覚に基づく、多くの可能な電源構成があります。

5.2 リチウムポリマー・バッテリーの直接接続

Intel® Edisonへの最もシンプルなバッテリー駆動接続は、図22で示すように、直接バッテリーをVSYSへ接続することです。しかし、この構成は推奨されません。なぜなら、充電システムにおいて、充電電流とトータルのシステム電流を見分けることができないためです。

注記: Intel® Edisonの起動を電源スイッチ信号のPWRBTN#(17ピン)をLowに保つことによって防止するのであれば、入力はバッテリー充電電流であると想定することができます。

図22 Intel® Edisonとリチウムポリマー・バッテリーの直接接続の例

5.3 ダイオードまたはFETによるリチウムポリマー・バッテリーの隔離

この構成では、通常の動作においてIntel® Edisonはダイオードによる電圧降下の影響を受けます。この構成はバッテリー切れであってもシステムのブートを許容します。この構成は充電を制御するために追加のピンを外部回路に必要とします。ダイオードをpチャネルFETに置き換えてゲートをLowにすることで、ダイオードによる電圧降下と電力損失を避けることができます。このような機能はTexas Instruments* BQ24073を採用する再充電器において見られます。

図23 Intel® EdisonにFETによる隔離を備えたリチウムポリマー・バッテリーの例

5.4 USB VBUSへの接続

直接USBによる電源供給でIntel® Edison Compute Moduleを稼働させることはできません。USBの電源仕様(4.75V~5.25V)はIntel® Edisonの安全な動作範囲を超えています。USB電源はLDO、小型降圧型スイッチング・コンバーターまたはTexas Instruments* BQ24074のような再充電器で降圧しなければなりません。

5.5 コールド・ブート・シーケンス

図24にコールド・ブート(電源の入っていない状態からの起動)からの信号シーケンスを示します。

注記: 図24のRESET#信号はRESET_OUT#として70ピン・コネクターの36ピンでアクセスすることができます。

図24 Intel® Edisonのコールド・ブート・シーケンス

6 Intel® Edison物理仕様

図25 Intel® Edisonモジュールの物理寸法(PCBを上から見下ろした図)

70ピン・コネクターの1ピンはコネクターの右下角に位置します。2ピンの位置はコネクターの向こう側の左下角に位置します。これによって69ピンはコネクターの右上角に位置し、そして70ピンはコネクターの左上角に位置します。コネクターの中心点は図面で指定します。

2つの取り付け用の穴の直径は2.0 mmです。ネジ山は3.0 mm未満であるべきです。取り付け用の穴はT1.6 mm ネジとして設計されました。

注記: オンボードのチップ・アンテナが右下角にあります。図面では“ANTENNA KOZ”として記載されています。ユーザーによって設計された拡張PCBは、アンテナ占有域の近くにコンポーネントや金属製の物体を配置すべきではありません。

Intel® Edisonの両面のほとんどのコンポーネントがシールドでカバーされています。PCBの両面から測定するボード両面のシールドの高さは約1.5 mmです。PCBの厚さは0.8 mm ±0.1 mmとして指定されています。したがって、Intel® Edisonの合計最大厚は3.9 mmです。これらの値はDVTモジュールで確認することができます。

7 レイアウト

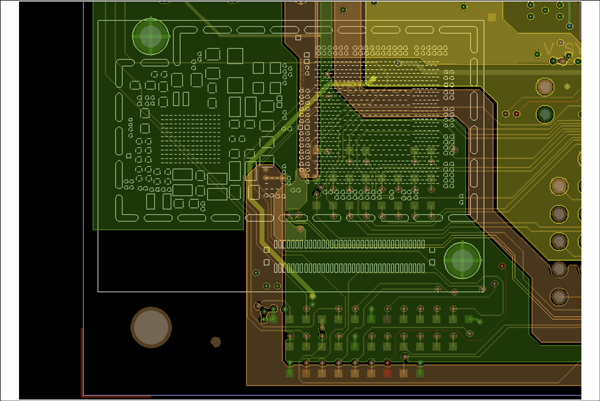

7.1 アンテナ占有域

アンテナの下とその周辺の領域は、すべてのコンポーネント、ルート、およびグラウンド面から解放状態になければなりません。

例えばIntel® Edison Kit for Arduino*のトレース・レイヤーでアンテナ占有領域として示されている、Intel® Edison Compute Module DXFの空白部分がそれです。図26を参照ください。

図26 アンテナ周辺領域

7.2 SDカード、I2S、SPI、I2Cのレイアウト

表33 SDカードのレイアウト

| 信号パラメーター | 距離 (mm) | 標準 (mils) |

|---|---|---|

| 合計長 L1 | 0.254 ~ 101.6 mm | 10 ~ 4000 mils |

| DATA/CMD/CTRL ~ CLK ピンとピンの間の長さの最大不整合 | ±2.54 mm | ±100 mils |

| 最小のメイン・ルート間隔比率 | 60 × 60 μm. 1:1 トレース 幅/間隔. | |

| CLK ~ DATA/CMD/CTRL 突合せ | ±200 mils | |

| シングル・エンデッド・インピーダンス特性 | 42 ~ 45 Ω (±10%) | |

| 負荷キャパシタンス | 2 ~ 5 pF | |

注記: 1) SPIでは、合計の長さは6000 mils.

2) I2Cでは、合計の長さは8000 mils.

7.3 DXFのレイアウト

以下の組み込みファイルは、図27の画像が示すように、Intel® Edison Compute ModuleのDXFです。

注記: KOZは占有領域です。

図27 DXFによるレイアウト

7.4 PTC ENMファイルによるレイアウト

図28 PTC ENM画像

図29 H383485-300

8 取り扱い

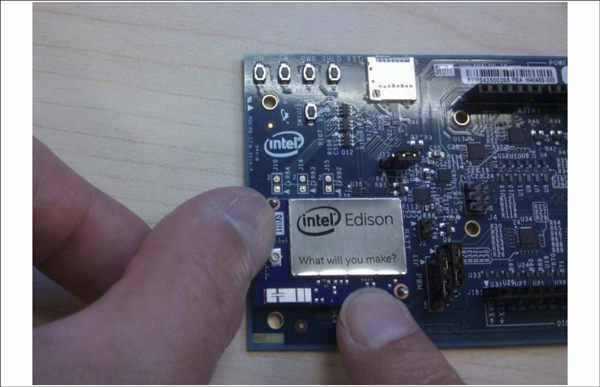

Intel® EdisonモジュールをArduino*ボードに組み立てる際には、PCB端の近くにIntel® Edisonモジュールを取り付けます。シールドを掴んだり圧力を加えることは避けてください。Intel® Edison ArduinoボードにIntel® Edison Compute Moduleを噛み合わせるように、コネクターのその上と左上角を図30で示すように押してください。

図30 Intel® Edisonモジュールの挿入

まとめ

今回のこのドキュメントを日本語でまとめるにあたり、約9日の時間を要しました。元々はリビジョン002のドキュメントを8割以上の量で完成させていたのですが、それを公開しようかと思ってちょっと検索してみたら004が公開されていました。じゃあ、それを取り込まなければならないな…、と思ったのですが、002に対して004は2倍の情報量があり、思わぬ苦戦をした感じです。

また、私はソフトウェア側の人間であり、今回まとめたこのドキュメントのようなハードウェア側の知識は足りていません。おそらくは読まれた方々は、いろいろな指摘、指導などあるかと思います。メモの文頭に書いた内容を念頭に、その情報をいただければと思います。

今回のこの情報が少しでも皆様のお役にたてば幸いです。

日本語ドキュメント 改定履歴

2015年2月15日

初版

2015年2月19日

- 一部の英文仕様書名に日本語訳をあてていなかったのを併記に修正しました。

- 電気特性関連の一部誤訳を修正しました。

- 本ドキュメントを示す「(このドキュメント)」の表示場所を修正しました。

- 複数の対象がある場合で単数に言及する表現で、同等の対象に対して同等の表現を用いていないことがある不均衡表現を修正しました。

- 「Setup Time」(および類語、以下同)に日本語訳として「準備時間」としていた部分を原則として「セットアップ時間」に変更しました。

- 「Hold Time」(および類語、以下同)の日本語訳として「保持時間」としていた部分を原則として「ホールド時間」に変更しました。

後者2つの訳語の変更については「わかる半導体入門① 汎用ロジックIC / 東芝セミコンダクター社編 / 誠文堂新光社 / 2005年9月9日 第2刷 / 9784416104026 1922055014001」の表記を参考にしました。

2015年2月19日

- 表に枠線を追加しました。

2015年10月9日

USB関連に編集上の問題で欠けてしまった文章があったのを補いました。

2023年7月21日

HTMLのマークアップに誤りがあった点を訂正しました。

関連記事

- 「Intel Edison Breakout Board Hardware Guide」を日本語で読んでみる

- 「Intel Edison Kit for Arduino Hardware Guide」を日本語で読んでみる

- 有効にしたい場合は原書をご確認ください。

- インテル株式会社による表現がそうなっているので、それに合わせています。

- インテル株式会社による表現がそうなっているので、それに合わせています。

- 質問者の技術レベルに応じて必要な回答を用意するのは、非常に高いスキルと多くの時間を必要とするものです。私はこれらのサービスが可能な状態にはありません。

- 訳注: ここは原文に編集ミスと思われる部分があるので分けて書いています。

- 原文: ACA-agnostic legacy link

- 訳注: 原文では「Table 3」となっていますが、これは誤記であると考えられるため「表4」としています。

- 訳注: 原文では「transmit」のみで「data」がついていないのですが、日本語にするとバランスが悪いので「データ」を付加しています。

- 訳注: 原文では「3」がついていないのですが、端子名の方についているので説明側にも付与しました。

- 訳注: 原文では「GPIO buffer AC specifications」と直接の表名が記述されており、これは誤相互参照であると判断して表番号に置き換え、それに基づく記述に変更しています。